英语原文共 9 页,剩余内容已隐藏,支付完成后下载完整资料

具有数字补偿技术的12.77MHz 31 ppm /°C片上RC张弛振荡器

摘要

提出了一种采用数字补偿技术的12.77MHz片上RC弛豫振荡器的设计。为了保持频率稳定性随温度和电源电压变化的变化,在该系统中开发了通过数字反馈环路进行环路延迟调整的方法。为了生成用于数字校准的片上基准,添加了一个复制比较器。片上张弛振荡器采用0.18mu;mCMOS工艺制造。补偿后,在minus;30至120°C的温度范围内,测得的输出频率变化为31 ppm /℃。电源电压在0.6 V至1.1 V范围内的频率变化为plusmn;0.5%/ V。启用数字补偿模块时,在0.9V电源电压下测得的总功耗为56.2mu;W。经过数字补偿后,可以关闭补偿模块以节省功耗,并且主振荡器的功耗仅为12.8mu;W。

索引词:数字校准,频率稳定性,环路延迟,低功耗,张弛振荡器,温度系数。

- 引言

片上参考时钟发生器在低成本和低功耗的片上系统(SoC)中引起了很多关注,例如可植入生物医学设备和无线传感器节点[1]。作为便携式医疗设备的时钟发生器或计时器,驰豫振荡器的频率稳定性对温度和电源电压变化的影响是片上振荡器的关键指标[2]。由于对R和C温度系数,与温度有关的比较器失调电压,与温度有关的比较器和逻辑延迟的严格要求,要实现具有对温度的高频稳定性的片上RC弛豫振荡器具有挑战性。可以通过使用不同的电阻器类型[3],[4]或使用专用的温度系数注入器[5]来降低RC温度系数。在千赫兹范围内,比较器失调(Vos)通常是主要挑战,可以使用斩波器技术来消除失调电压,如[6]和[7]中所述。此外,在[5]和[8]中,开关点不灵敏的振荡器架构设法减少了Vos的影响。对于较高的频率输出(超过10 MHz),比较器延迟(tcomp)的温度依赖性通常是主要瓶颈。

在过去的几年中,报告了许多减少tcomp温度依赖性影响的研究。在[3],[4]和[9]中,通过使用电压平均反馈(VAF)技术调整比较器的参考电压来实现频率控制。所有这些设计都使用模拟积分器反馈环路来实现频率稳定性,但主要是以功耗为代价的。文献[10]报道了采用恒电荷减法技术的张弛振荡器,它使用低功耗时间跟踪拓扑从时钟周期中消除了tcomp。但输出频率受到限制(11 Hz)。在[11]-[14]中,报道了基于频率锁定环(FLL)技术的环形振荡器[15]。这些工作从振荡回路中省去了传统的比较器。低带宽超低功率放大器可以在FLL中使用,因为它随温度变化仅影响压控振荡器(VCO)。在[16]中,在张弛振荡器中实现了前馈周期控制技术。通过使用升压充电技术对其进行测量和去除,可以降低tcomp的影响。但是,测量tcomp的周期控制器几乎使面积和功率增加了一倍。在[17]中展示了一种基于全数字PLL的频率补偿技术。但是,这种方法要求为PTAT振荡器提供多个耗电的片上加热器。

为了解决上述缺点,本文提出了一种具有低温度敏感性和低功耗的12.77MHz片上弛张振荡器[18]。与[3],[4],[9]部署模拟积分器以补偿频率变化不同,所提出的设计使用数字反馈环路来调整环路延迟以实现频率稳定性。以下各节将提供这项工作的详细信息。在第二部分中,讨论了传统的张弛振荡器架构和所提出的设计。第三节讨论了电路的设计和实现。还详细讨论了新颖的数字补偿方法。最后,测量结果和结论分别在第四节和第五节中介绍。

二:张弛振荡器的体系结构设计技术

- 常规的张弛振荡器

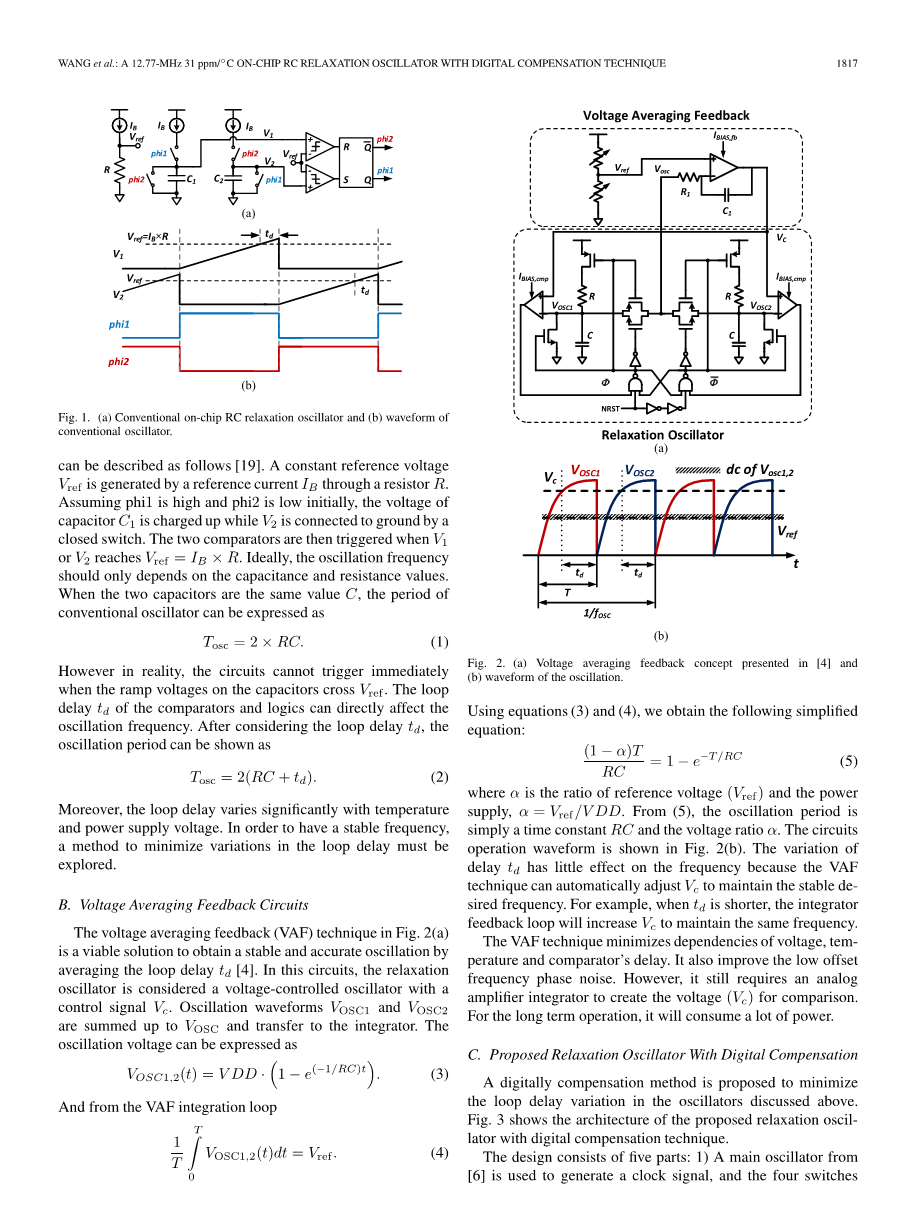

图1示出了常规张弛振荡器的框图和时序图。振荡器的操作可描述如下[19]。

图1.(a)常规片上RC弛豫振荡器,以及(b)常规振荡器的波形。

基准电流IB通过电阻R产生恒定的基准电压Vref。假设phi1高而phi2最初低,则电容器C1的电压被充电,而V2通过闭合开关接地。然后,当V1或V2达到Vref = IBtimes;R时,将触发两个比较器。理想情况下,振荡频率应仅取决于电容和电阻值。当两个电容器的值C相同时,传统振荡器的周期可以表示为:

Tosc = 2times;RC (1)

但是实际上,当电容器上的斜坡电压超过Vref时,电路无法立即触发。比较器和逻辑的环路延迟td可以直接影响振荡频率。考虑环路延迟td之后,振荡周期可以表示为

Tosc = 2(RC td) (2)

此外,环路延迟会随温度和电源电压而显着变化。为了获得稳定的频率,必须探索一种使环路延迟变化最小的方法。

B.平均电压反馈电路

图2(a)中的平均电压反馈(VAF)技术是通过平均环路延迟td [4]来获得稳定而准确的振荡的可行解决方案。在该电路中,张弛振荡器被认为是具有控制信号Vc的压控振荡器。振荡波形VOSC1和VOSC2总计为VOSC,并传输到积分器。振荡电压可以表示为

(3)

并从VAF集成循环

(4)

图2.(a)[4]中表示的平均电压反馈概念,(b)振荡波形。

使用方程式(3)和(4),我们得到以下简化的方程式:

(5)

其中alpha;是参考电压(Vref)与电源的比率,alpha;= Vref / V DD。根据(5),振荡周期仅是时间常数RC和电压比alpha;。电路工作波形如图2(b)所示。延迟td的变化对频率影响很小,因为VAF技术可以自动调节Vc以保持稳定的所需频率。例如,当td较短时,积分器反馈环路将增加Vc以保持相同的频率。VAF技术最大程度地减少了电压,温度和比较器延迟的依赖性。它还改善了低偏移频率的相位噪声。但是,仍然需要一个模拟放大器积分器来创建电压(Vc)进行比较。对于长期运行,它将消耗大量电能。

C.建议的具有数字补偿的张弛振荡器

提出了一种数字补偿方法以最小化上述振荡器中的环路延迟变化。图3显示了采用数字补偿技术的弛张振荡器的架构。

该设计包括五个部分:

1)[6]的主振荡器用于生成时钟信号,此处的四个开关用作斩波器结构,以消除比较器的失调。例如,假设振荡器具有偏移Vos,则相位phi = 0的持续时间会增加。但是,相反的相位phi = 1将减少相同的值; 因此,总振荡周期是恒定的。

2)参考脉冲产生电路提供数字校准参考脉冲。

3)环路延迟调整模块由几个不同的延迟线组成,这些延迟线由一些反馈位控制。如(2)所示,环路延迟将影响振荡频率。在这项工作中,数字反馈环路将调整环路延迟以补偿输出频率。如果输出频率高于期望的频率,则会增加环路延迟以降低频率。

4)数字补偿电路由两个时间数字转换器(TDC)和一个数字校准算法组成。两个TDC用于将来自振荡周期和参考脉冲的时序信息转换为数字位。然后,数字校准模块处理这些位,以提供一些反馈控制位来调整延迟单元。

5)绝对温度互补(CTAT)电流偏置发生器提供系统中的所有偏置电流。

由于采用0.18mu;mCMOS工艺的低电源电压设计(0.6 V至1.1 V),所有电路都在接近阈值区域工作。当温度降低时,电路的传播延迟变大。因此,选择CTAT电流源来补偿这种影响。

图3.带有数字补偿反馈回路的张弛振荡器的架构

图4示出了振荡器的工作波形。比较基准电压Vref1由偏置电流IB和恒定电阻器R1产生。在相位phi = 1期间,电流将对电容器C充电以生成将用于参考脉冲生成的斜坡信号Vramp,并将在下一节中进行讨论。当节点VC1与节点VC2相交时,phi在某个延迟时间后变为零,该延迟时间是比较器延迟(tcomp)和数控延迟单元(tdig)的总延迟。因此,两个比较器输入被交替取反。振荡周期可以表示为2(RC tcomp tdig)。

所提出的方法的优点可以总结如下。首先,与[3],[4]和[9]中的模拟积分器环路来比较比较器的参考电压相比,所提出的校准环路避免了需要耗电功率放大器的积分器的使用。相反,仅需要一个比较器。其次,频率是数字调谐的。这意味着在校准过程完成后可以关闭所有补偿段,从而在长期运行中节省了大量功率。由于环境温度在应用中不会急剧变化,因此数字补偿电路会定期打开以跟踪温度变化。第三,自补偿主要是在数字领域,与使用模拟补偿相比,在CMOS工艺技术中实际上可以更好地扩展。此外,数字补偿部分可以与更大的DSP或SoC系统合并以减少开销。但是,由于采用了数字控制方法,因此与模拟方法相比,调谐步骤是不连续的。分辨率由延迟单元的最小值确定。

图4.提出的张弛振荡器的波形

三:拟议振荡器的电路级技术

- 参考脉冲产生

在所提出的自校准系统中,与敏感环路延迟无关的参考信号是强制性的。如图3所示,在片上数字补偿技术中,附加的参考电压(Vref2)和复制比较器(COMP2)用于生成参考脉冲。脉冲发生器的波形在图5中给出。最初,当时钟信号phi为高时,电容器C1由电流源充电,并且所产生的斜坡电压Vramp连接至COMP1的负节点。假设比较器的延迟为tcomp,图3中的数控延迟单元为tdig。COMP1触发后,V1的脉冲宽度可以表示为:

t1 = R1 ・ C tcomp. (6)

同时,信号Vramp也连接到附加比较器COMP2的正节点。当COMP2从零变为一时,时间t2也表示为:

t2 = R2 ・ C tcomp (7)

这些过程使我们能够从两个t1和t2之间的时间差中获取参考脉冲,其中:

Pref = t1 minus; t2 = (R1 minus; R2) times; C (8)

从(8)可知,脉宽表达式中显然没有延迟参数。脉冲宽度的周期仅与电阻器和电容器有关。因此,它用作数字补偿算法的参考时间值。

实际上,参考脉冲是由两个比较器的输出V1和V2之间的差异产生的,这是两者的与函数。同一比较器内的高到低和低到高转换期间的失配对参考脉冲影响很小。考虑两个比较器之间的非理想失配时,参考脉冲可以表示为

Pref = (R1 minus; R2)C (Vos1 minus; Vos2) tcomp1 minus; tcomp2 (9)

其中Vos1和Vos2是两个比较器的偏移电压。为了最小化偏移电压和比较器延迟失配,在布局图绘制过程中精心设计了两个比较器。图6(a)显示了在0.9V电源电压下,过程和失配对基准脉冲宽度的影响。基于300个蒙特卡洛模拟,平均脉冲宽度为20.52 ns,标准偏差为0.971 ns。图6(b)显示了在-55℃至135℃温度范围内的平均值和标准偏差变化。在整个温度范围内,参考脉冲的平均值为21.14 ns至20.42 ns,当温度高于-25℃时,标准偏差小于1 ns。在最终实现中,R1选择为150kOmega;,R2选择为80kOmega;。这两个电阻与P-poly电阻和N-plus电阻组合在一起以最小化温度系数。R1和R2的布局也合并在一起以减少不匹配。

- 建议的环路延迟变化的闭环数字校准

图7显示了反馈调整环路中的数字补偿算法。两个TDC用于将时间信息转换为数字域。芯片上会产生一个参考脉冲(Pref)进行校准,下一节将对电路电平进行描述。在这里,我们将数字补偿序列描述如下:

1)在振荡开始时,主振荡器启动,而其他模块禁用。这产生了振荡信号fout。

2)使能补偿环路后,将产生片内参考脉冲宽度(Pref)。TDC2测量Pref的脉冲宽度,将时间脉冲转换为数字代码N2。同时,通过TDC1获得N1,该TDC1测量输出频率fout的宽度。

3)理想情况下,输出频率的高电平脉冲可以表示为R1C tcon,其中tcon为常数,如果芯片的PVT改变时环路延迟保持稳定,则为延迟值。将这个公式与参考周期值进行比较[参见8],很容易推断出Pref和fout的高电平宽度之间的关系。因此,我们可以从N2估计频率值N 2。

4)将估计值N 2与实际值N1进行比较,如果N1大于N 2,则意味着频率慢于理想值。环路延迟由几个寄存器控制,以降低td。为了确保稳定的环路,当N1 = N 2或N 2-1时,我们假定补偿已完成。就循环稳定性而言,只有1位的余量。

5)补偿过程完成后,所有数字部分和参考脉冲发生器都可以关断,仅保留控制位,这些位存储在寄存器中以保持调谐环路延迟。校准电路将在下一轮补偿中被唤醒。实际上,N2具有5位分辨率,而N1和N 2均为8位数字代码。数控延迟单元为6位。由于采用了数字控制的延迟单元,可以关闭补偿部件,例如复制比较器,TDC等,以在补偿后节省功率。

图5.参考脉冲产生的工作波形。

图6.(a)室温下参考脉冲的蒙特卡罗模拟结果。(b)模拟平均值和sigma;对温度。

- 时间数字转换器和环路延迟控制器

图8显示了TDC和数字控制的延迟单元架构。TDC的简单结构在该设计中得到了利用[20]。时间信号通过一串延迟元件。为了增加延迟,定制了两个TDC中的每个延迟单元以增加其级延迟时间。触发器阵列用于采样每个延迟的信号。在建议的设计中,不需要fout和Pref的精确值。相反,参考脉冲与输出周期之间的映射关系将

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[240067],资料为PDF文档或Word文档,PDF文档可免费转换为Word