基于FPGA的多速率信号性能分析

摘要:多速率信号处理的一个重要组成部分是数字变频器的设计,它的实现主要基于插值和抽取,用来匹配基带之间的采样率和高频处理,尤其是在下变频处理。然而,对于实现多速率插值和抽取,数字滤波器的设计是非常重要的,这也是本文的重点。为了分析数字滤波器在多速率信号处理的性能,以下分别对普通的有限脉冲响应(FIR)滤波器和高效数字滤波器进行了讨论。普通的FIR滤波器采用汉明窗设计,而更有效的数字滤波器包括级联积分梳(CIC)和半带滤波器。在这个设计中,级联分为三个阶段,采样率转换因子是12,每个阶段对应转换因子是分别是3,2和2。这些设计方法在FPGA开发板上实现。在硬件资源占用和抽取信号幅度的错误率表明,在实时处理方面,高效数字滤波器优于基于汉明窗设计的数字滤波器。

关键字:多速率信号处理,抽取,汉明窗FIR滤波器,CIC,半带滤波器,FPGA

1介绍

多速率信号处理的关键技术是实现数字频率转换。在一般的通信系统中,基带信号的速度往往比中频信号(IF)低得多;为了匹配双方的采样率,毫无疑问,前者的采样率需要增加,这就相当于增加了采样点的数量。在接收过程中,信号从模拟到数字转换 (ADC)时过高的速率是很难直接提供给处理器进行处理;因此,提取这种方式被考虑来降低采样率。换句话说,离散采样信号被重新取样,最终,信号将下降到便于数据恢复的适当频率。所以插值和提取不仅是多速率信号处理的基础,也是设计数字变换器一个重要的理论支持。

当系统的功能性需求越来越多样化,电路的功能模块的设计变得越来越复杂,芯片处理速度的需求也越来越高。换句话说,传统的模拟电路不能满足整个设计的要求。这些大规模集成设备,例如FPGA和DSP高速信号处理器,现已被大力开发和推广,其特点是使用数字方式或软件来取代模拟电路。 目前,大多数的收发器涵盖了基带信号处理、数字变频和模拟转换。模拟变频旨在将高频模拟信号转移为合适的中频信号,它可以突破AD / DA等关键设备的限制,并且很容易获得低频基带信号。

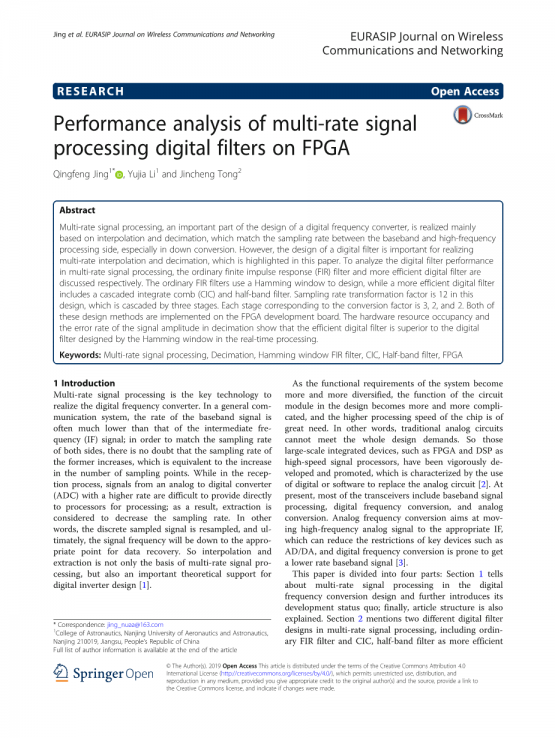

本文分为四个部分:第一部分讲述多速率信号处理中的数字变频器设计,并且进一步介绍其发展现状; 最后,将会阐述全文的结构。第二部分提到了多速率信号处理中两个不同的数字滤波器设计,包括普通FIR滤波器和CIC,半带滤波器作为更高效的数字滤波器,并提供它们的设计方案。第三部分给出了这两种数字滤波器在FPGA的详细的应用过程和仿真结果。第四部分是本文的结论。 本文主要以数字下变频为例;抽取将在之后的章节中讨论。 当采样转换因子较大时,单级滤波需要调整为多个阶段,所以三级滤波器级联设计来完成采样率转换因子12,每个阶段的抽取因素是3,2和2。完整设计框图如图1所示。

图1下变频取值级联框图

2方法

模拟是基于FPGA Altera Develop Board。所有结果由ModelSim仿真和Matlab2018计算得出。

3数字滤波器多速率信号处理的两种设计

多速率信号处理是一个值得讨论的重要技术。它由插值和取值组成,并在数字滤波器插值之后或者取值之前进行相应的设计。数字变频器的组成类似于模拟频率转换器,它主要包括数字混合机,数控振荡器(NCO)和低通滤波器。相比之下,模拟变频器的电路功能不够稳定,并且极大地受到温度的影响。然而,数字变频器不但能保证中频信号载波的正交性,而且还方便修改频率间隔和其他参数。此外,采样率转换的目的是匹配数据处理的速度,在接收机设计中更是如此;收到的中频信号频率在一定的取值之后会降低,从而可以减轻后续数据处理的压力。

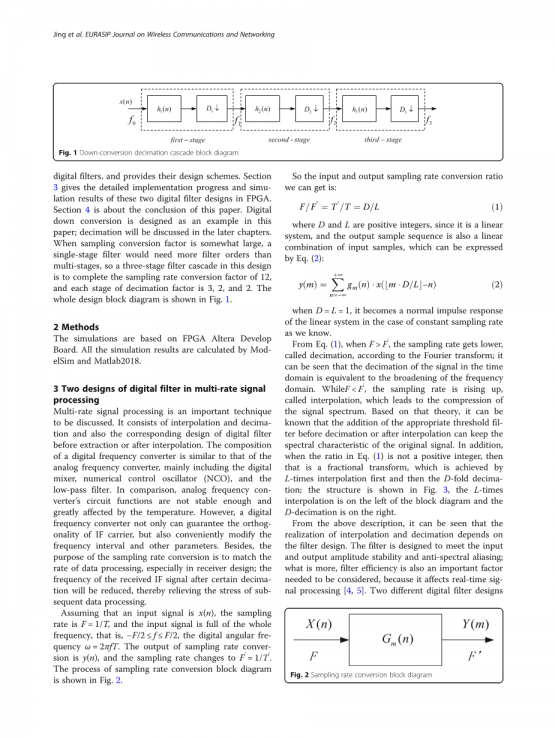

假设输入信号,采样频率F= 1 /T,输入信号充满了整个频率,即,数字角频率。采样率转换的输出,采样率变化Flsquo;= 1 /Tlsquo;。 采样率转换的流程框图如图2所示。

图2采样率转换框图

因此,输入和输出采样率转换比我们可以得到:

其中D和L是正整数,因为它是一个线性系统,输出样本序列也是一个输入样本的线性组合,如等式2所示:

当D=L= 1,它变成了一个我们所熟知的线性定值采样率冲击响应。

由等式1,根据傅里叶变换,当Fgt;Frsquo;,采样率较低,称为取值;可以看出,信号在时域的取值,就相当于频域的扩大。而若Flt;Frsquo;,采样率上升,称为插值,从而导致信号频谱的压缩。基于这一理论,就可以知道,在插值之后或者取值之前添加适当的阈值滤波就可以保持原始信号的频谱特性。此外,当等式1中的比率不是一个正整数,那么这是一个部分的变换,首先通过L次插值,然后D倍取值;如图3中所示的结构。L次插值在左边的框图,D倍取值在右边。

图3分级采样率转换框图

从上面的描述,可以看出插值和取值的实现依赖于滤波器的设计。过滤器设计用于满足输入和输出振幅稳定和防止频谱混叠;更重要的是,过滤效率也是需要考虑的一个重要因素,因为它会影响实时信号处理。两个不同的数字滤波器的设计将在以下部分讨论,普通的数字滤波器设计采用汉明窗FIR将首先被阐述,然后是更高效的数字滤波器,包括CIC,半带,之后讨论CIC补偿滤波器。

3.1汉明窗FIR取值滤波器设计

从图1可知,每个阶段过滤后的采样率为,可以通过等式3计算:

在系统仿真中,通带截止频率的输入信号设置为2.1 MHz,为了防止取值之后频谱扩展造成的频谱混叠,最后阶段的通频带和过渡区设计如下:

以下二级和一级滤波器的通带和转换方法的设计应确保每个级的通带相同,而陡峭的过渡区直接将影响滤波器的设计阶数。设计符合的抗混叠滤波器,使得第二过渡区可以计算:

同样,第一阶段的过渡区如下:

上面的设计给出了通带、阻带和每个阶段的输出采样率。一个过滤器带外衰减不低于55分贝是必需的;根据这些,过滤器的阶数可以由汉明窗的特点计算。具体公式如下:

其中,和分别为通带和阻带截止频率。因此,计算每个阶段所需的滤波器,将会有更多的取值高效数字滤波器设计。

可以看出,第三阶段的汉明窗数字滤波器的阶数是261,这导致繁琐的计算和较差的实时性。因此,一个更高效的数字滤波器被纳入考滤。CIC和半带滤波器之类的高效过滤器的在度速率信号处理中很常见,如下将分别介绍其特点。

3.2更高效的数字滤波器

3.2.1 CIC滤波器

CIC被称为级联积分梳,是一种常用的高效滤波器,主要应用在取值因素并不是2的幂的场合。因其效率高的原因是它的系数是1,所以它不需要乘法器。正因为如此,它通常用于多速率转换的高速信号处理。

CIC滤波器的脉冲响应如下:

其中D是取值因素,也代表CIC的阶数,z平面上的传递函数是:

等式9可以被看作是一个由两部分组成的级联信号相乘的结果; 前者是一个积分器,后者是一个级联积分梳,这是CIC名称的起源。框图如图4所示。

图4 CIC实现结构

对于公式9,替换,我们得到最终的振幅频率响应:

由此,CIC滤波器的幅频曲线可以得到(图5)。

图5 CIC振幅频率曲线

当D1,第一部分振幅是:

从等式11我们可以知道主、副幅度之比是3pi;/ 2;也就是说,旁瓣只比主瓣小不到13.46 dB。 因此,单一的CIC滤波器的旁瓣振幅很大,通常不能满足系统的要求。为了减少旁瓣衰减,多级CIC滤波器级联则可以用于帮助设计; 每增加一个阶段的CIC滤波器,旁瓣衰减将减少13.46 dB。在这个设计中,五个CIC滤波器级联使得第一个旁瓣衰减67 dB,基本上可以满足系统要求。

3.2.2半带滤波器

图6显示了半带滤波器的幅频曲线。 在图6中,和分别是通带纹波和阻带纹波,和分别是通带截止频率和阻带截止频率。半带滤波器具有以下属性:

图6半带滤波器频谱特性

结合半带滤波器的频谱特性,当很小时,对于一个双重的抽取,频谱被两次拉伸,然后是相位被移动了2pi;。尽管频谱从pi;/ 2到与[,pi;/ 2]区间的信号相混叠,但是位于通频带信号[0,]可以恢复,所以半带滤波器可以用于双重抽取。当取值因素很大并且和形式相似,就可以实现M级半带滤波器级联。

半带滤波器能够确保相位线性并且甚至能够使滤波器的系数也对称,这使得它可以证明所有除去中心点的系数都是零,这大大降低了滤波器的计算量,提高了滤波处理实时性。

3.2.3 CIC补偿滤波器

接收到的信号被数字变频器处理后可以恢复,但是需要一个合适的滤波器设计参数,以保证信号波形形状不会明显改变,同时也需要保持信号的振幅在容错范围内;因此,输入和输出的增益需保持在0 dB。

CIC滤波器不同于一般FIR数字滤波器;从图5的曲线中可以看出,通频带很窄,而且不是单调的;因此,它不能在大部分应用中直接使用,所以有必要设计一个相应的补偿滤波器,以保证CIC波形在通带是单调的。N级 CIC滤波器级联的频率响应函数可以按照如下表示(微分延迟M默认设置为1):

其中,代表了取值前采样率,采样率变换因子,作为CIC滤波器的序列。参数N越大,通频带越不均匀,所以在通频带需要一个逆频率的响应来校正这种不平衡。因此,根据等式14,可以推导出CIC补偿滤波器的响应函数。

根据等式15,当R→infin;,补偿滤波器可以近似为一个逆辛格函数。

3.2.4设计方案

在这个实验中,数字下变频器作为一个范例,并且假设解调后的信号是两种正弦信号; 它们的频率是1MHz和1.5 MHz。解调数字采样率是60 MHz,后端DSP的处理速度是5 MHz,所以采样率转换因子是12。设计一个三级级联设计来完成下变频多速率处理。CIC过滤器放在第一阶段是由于其非常适合高速处理情况,并且可达到三倍采样率转换;第二个阶段是CIC补偿滤波器,用于减少CIC滤波器后的非线性影响,因素是2;最后一个阶段是用半带滤波器,拥有两倍采样率速降;整个下变频过程如图7所示。

图7下变频设计框图

补偿滤波器设计使用的是MATLAB的fir2函数,系数是18位定点表示;同时,通带截止频率设置为2.1 MHz,过滤器的阶数计算为61。图8展示了CIC滤波器、CIC补偿滤波器和整个频率响应。可以看出中投不是平的频率响应在通频带在赔偿之前,和之后适当补偿滤波器设计,整个反应是相当稳定的,这样滤波器输出的结果似乎没有太多的波动后适当的数据截断。

图8 CIC滤波器,补偿滤波器,整体频率响应

同样,半带滤波器的系数由MATLAB中“firhalfband”函数生成,并且也由18位定点表示。

4两个多速率数字滤波器的设计实现

4.1汉明窗数字滤波器的FPGA实现

根据系统需求,滤波器通带截止频率为2.1 MHz,并且带外衰减小于50dB。所以每个阶段滤波器的特性曲线如图9所示。通带、阻带截止频率和采样率在滤波器各个阶段的图中给出。汉明窗的基础公式在第二部分已经给出,每个阶段滤波器的阶数计算结果分别为42、40和261。可以看出第一阶段滤波器的过渡带比较窄,所以所需的过滤器的阶数很大,需求的存储资源也非常大,这将大大影响过滤器处理速度。因此,每个过滤器取值前的参数如表1所示。

图9抽取的每个阶段汉明窗滤波器设计

表1取值前各滤波器参数

|

滤波器参数 |

第一阶段 |

第二阶段 |

第三阶段 |

|---|---|---|---|

|

通带截止频率(MHz) |

2.1 |

2.1 |

2.1 |

|

阻带截止频率(MHz) |

17.5 |

7.5 |

2.5 |

|

过滤器的阶数 |

42 |

40 |

261 |

根据上面的汉明窗滤波器的设计,在硬件仿真,输入通过测试输入写入激励测试文件,并由ModelSim仿真输出结果。有240个二进制补码数据值代表了两个的信号作为测试输入;输出也是二进制补码滤波后的信号。仿真工具的输入和输出的波形基本上是相同的,峰幅度也接近。

4.2高效过滤器的FPGA实现

CIC滤波器只

英语原文共 9 页

资料编号:[6002]