英语原文共 63 页,剩余内容已隐藏,支付完成后下载完整资料

ST7580

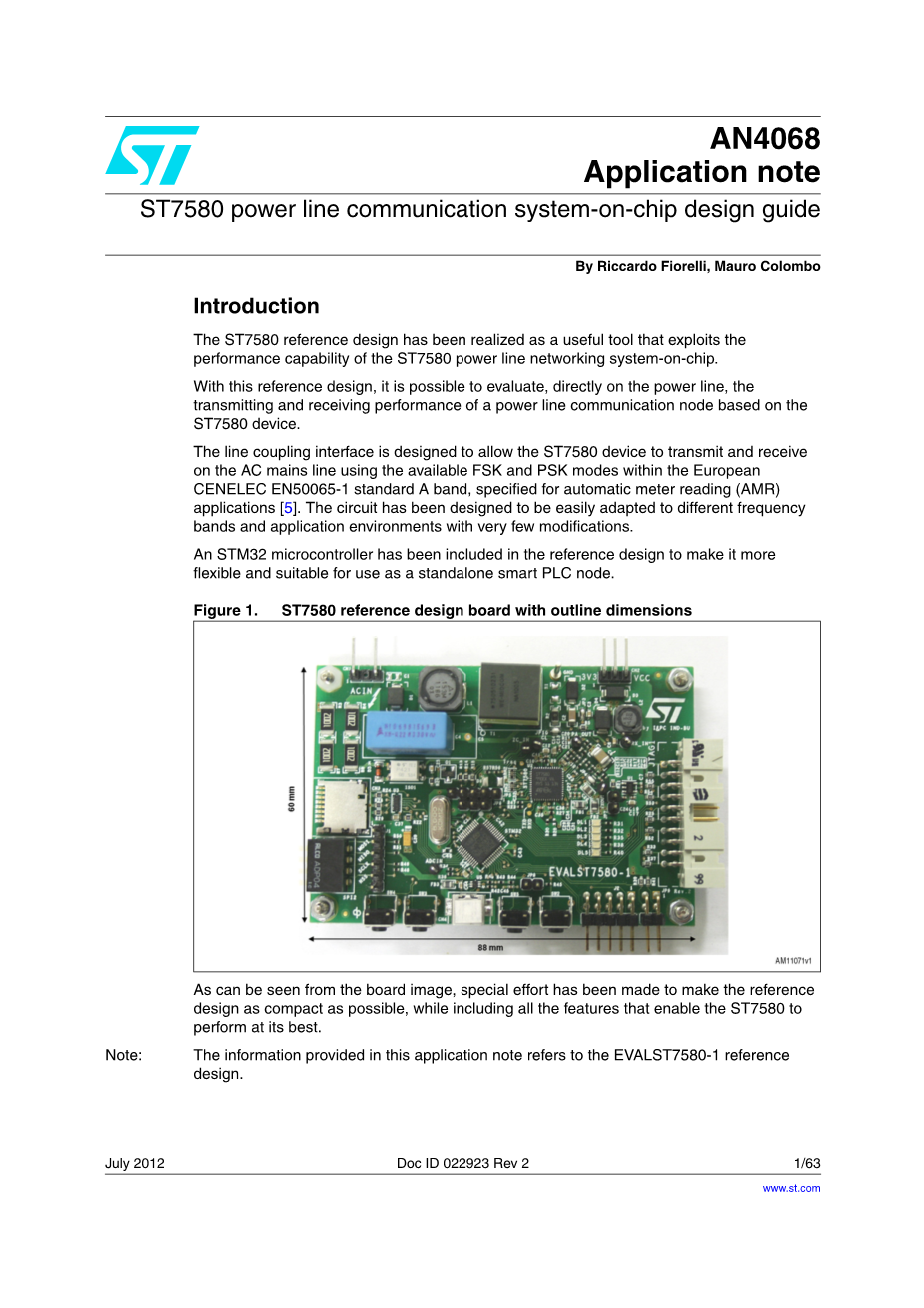

FSK,PSK多模电力线网络片上系统

9)4)31 7[7[1.0 48/

(SLWFK 0.50)

特征

- 完全集成的窄带电力线网络片上系统

-

具有嵌入式交钥匙固件的高性能PHY处理器具有:

- B-FSK调制高达9.6 kbps

- B-PSK,Q-PSK,8-PSK调制可达

28.8 kbps

-

- 双通道操作模式

- 卷积纠错编码

- 信噪比估计

- 具有PNA模式的B-PSK针对脉冲噪声

-

协议引擎嵌入交钥匙通信协议

- 构筑服务

- 错误检测

- 嗅探器功能

- 主机控制器UART接口速度高达57.6 kbps

- 基于AES-128的认证和机密性服务

-

完全集成的模拟前端:

- ADC和DAC

- 数字传输电平控制

- 带自动增益控制的PGA

- 高灵敏度接收器

数据表 - 生产数据

-

用于线路驱动的全集成式单端功率放大器

- 高达1 A RMS,14 V pp输出

- 可配置的有源滤波拓扑

- 非常高的线性度

- 内置温度传感器

- 电流控制功能

- 8至18 V功率放大器电源

- 3.3 V或5 V数字I / O电源

- 过零检测

- 适用于EN50065,FCC第15部分和ARIB兼容应用

- 通信载波频率可编程至250 kHz

- VFQFPN48 7x7x1.0 48L裸露焊盘封装

- -40°C至 105°C的温度范围

应用

- 智能计量应用程序

- 街道照明控制

- 指挥和控制网络

描述

ST7580是一款灵活的电源线联网片上系统,将高性能PHY处理器内核和协议控制器与完全集成的模拟前端(AFE)和线路驱动器相结合,可实现可扩展的面向未来的低成本单芯片,窄带电力线通信解决方案。

表1.设备摘要

|

订单代码 |

包 |

打包 |

|

ST7580 |

VFQFPN48 |

管 |

|

ST7580TR |

磁带和卷轴 |

2016年5月 DocID022644修订版2 1/33

这是关于产品全面生产的信息。 www.st.com

内容

1 设备概述 4

2 引脚连接 5

引脚说明 7

3 最大额定值 11

3.1 绝对最大额定值 11

3.2 热数据 11

4 电气特性 13

5 模拟前端(AFE) 19

5.1 接待路径 19

5.2 传输路径 20

5.3 功率放大器 20

5.4 电流和电压控制 21

5.5 热关断和温度控制 22

5.6 过零比较器 22

6 能源管理 23

接地连接 24

7 时钟管理 27

8 功能概述 27

参考 28

9 物理层 29

9.1 PSK调制 29

9.1.1 PSK模式 29

9.1.2 PSK物理帧 30

9.2 FSK调制 30

9.2.1 FSK选项 30

9.2.2 FSK物理帧 32

9.2.3 FSK设置 32

9.3 通道和调制选择 32

10 数据链路层 34

10.1 数据链接帧 34

10.2 错误检测和嗅探模式 34

10.3 安全服务 34

11 包信息 35

11.1 VFQFPN48(7 x 7 x 1.0 mm)封装信息 35

12 修订记录 38

DocID022644修订版2 3/33

设备概述

采用多电源技术和最先进的VLSI CMOS光刻技术制造的ST7580基于双数字内核架构(PHY处理器引擎和协议控制器内核),以高水平的灵活性确保出色的通信性能无论是开放标准还是定制实施。

当需要安全通信时,可在芯片上提供具有可定制密钥管理的HW 128位AES加密模块。

片上模拟前端具有模数转换和数模转换功能,自动增益控制以及集成功率放大器,可提供高达1 A RMS的输出电流,使ST7580成为用于电力线通信的独特系统芯片。

线耦合网络设计也被简化,导致BOM成本非常低。

在保持功耗和信号失真水平非常低的同时,可以保证稳健和可执行的操作; 这使得ST7580成为最严格的应用要求和监管标准合规的理想平台。

图1.框图

ZC_IN

VCCA(5V)

RX AFE

BPF

PGA ADC

协议控制器

BPF

增益控制

DAC

TX AFE

ON-CHIP

线驱动程序 回忆

输出电流控制

热管理

-

时钟管理

零交叉检测

能源管理

定时器

DDS

看门狗

PHY处理器

128位AES

SPI0/UART

ON-CHIP

回忆

AM02502v1

VDD_PLL XIN XOUT(1.8V)

VDD(1.8V)

VCC(8-18V)

VDDIO(5 / 3.3V)

BR1 BR0

PL_RX_ON

PL_TX_ON

RX_IN

TX_OUT

T_REQ RXD

TXD

PA_OUT

PA_IN PA_IN- CL

4/33 DocID022644修订版2

XOUT GND VSSA VDD_PLL

VCCA ZC_IN RX_IN TX_OUT PA_IN PA_IN-

CL

VCC

引脚连接

图2.引脚分布顶视图

AM02503v1

13 14 15 16 17 18 19 20 21 22 23 24

36 CL_SEL

35 VSSA

34 VDDIO

33 GND

32 NC

31保留0

30 NC

29 NC

28 VDDIO

27 VDD_REG_1V8

26 PA_OUT

25 VSS

TXD 1

RXD 2

VDDIO 3

TRSTN 4

TMS 5

GND 6

TCK 7

TDO 8

TDI 9

重置10

VDD 11

XIN 12

48 47 46 45 44 43 42 41 40 39 38 37

保留5保留4 VDD

GND RESERVED3 RESERVED2 RESERVED1 PL_TX_ON BR0

BR1 T_REQ

PL_RX_ON

引脚说明

表2.引脚说明

|

销 |

名称 |

类型 |

重置状态 |

内部上拉 |

描述 |

|

1 |

TXD |

数字输出 |

高-Z |

残 |

UART数据输出。 需要外部上拉至VDDIO |

|

2 |

RXD |

数字输入 |

高-Z |

残 |

UART数据输入 |

|

3 |

VDDIO |

功率 |

- |

- |

3.3 V - 5个VI / O电源 |

|

4 |

TRSTN |

数字输入 |

输入 |

启用 |

系统JTAG接口复位(低电平有效) |

|

5 |

TMS |

数字输入 |

输入 |

启用 |

系统JTAG接口模式选择 |

|

6 |

GND |

功率 |

- |

- |

数字地面 |

|

7 全文共15095字,剩余内容已隐藏,支付完成后下载完整资料 资料编号:[14855],资料为PDF文档或Word文档,PDF文档可免费转换为Word |