英语原文共 14 页,剩余内容已隐藏,支付完成后下载完整资料

一种25分贝具有自适应数字预失真和有效功率控制的用于WCDMA/EDGE/OFDM的数字调制CMOS功率放大器。

摘要

本文提出一种基于1.2伏、0.13微米的SOI CMOS结构的数字调制功率放大器(DPA),这种结构在多标准、多波段的极性发射机中使用。它通过数字控制127个一元加权和三个二元加权基本增益单元的阵列来执行输入RF载波的直接幅度调制。DPA基于一种新颖的两级拓扑结构,这种结构能完成800 MHz到2Ghz的无缝操作,并且全功率效率大于40%,最大包络功率为25.2分贝。

利用自适应数字预失真可以实现DPA线性化。因此,该电路能够以1.9 GHz的频率、38%的效率和高于10分贝在所有光谱规格上重建21.7分贝的WCDMA/EDGE信号。作为数字调制技术的结果,WCDMA信号的效率高于20.1%,其峰值功率比高达10.8 分贝。

一个高10位的标称分辨率可以实现宽量程的TX功率控制,这大大减少了的静态消耗,只有10毫瓦。因此,通过70分贝功率控制范围可以获得16.4%的CDMA平均效率,同时符合所有的光谱规范。

索引词——所有数字、CMOS、数字预失真(DPD)、数字发射机、数字调制功放(DPA)、动态偏置、边缘、高效放大器、IEEE802.16、多波段、多模式、多标准、多模、多模、多模、多频、多频、极性发射机、功率放大器(PA)、射频集成电路(RFIC)、软件定义无线电、TX功率控制、WCDMA、WiMAX。

Ⅰ.简介

综合射频谱带的过度拥挤导致标准化机构利用新的频率窗口和调制格式进行无线通信。由于这个原因,最近有相当多的研究工作致力于执行多标准无线电模块[1], [2]。最有希望实现这一远大目标的技术平台是CMOS,因为它具有无可匹敌的适合大规模集成的能力。最近,新的数字密集型无线电架构已经成为研究的原型或商业产品,这种架构中CMOS技术的低射频性能通过数字信号处理(DSP)得到补偿[3]。

在所有射频电路块中,设计一个合适的CMOS功放(PA)仍然是实现高集成CMOS发射机(TX)最复杂的挑战之一。实际上,为了有效地利用可用的射频带宽,目前的无线标准采用了增加复杂度的调制格式,例如GSM演进(EDGE)、宽带码分多址(WCDMA)和正交频分复用(OFDM)。在所有这些情况下,产生的射频信号具有一个不恒定的包络线,因此需要线性CMOS功放。不幸的是,传统PA电路的效率通常只有在额定峰值输出功率(POUT)时才高,而如果峰值输出功率被抑制以适应调幅,则它的效率会大大降低。这种线性效率的取舍在CMOS中尤其严重[4]。

为了实现灵活高效的TX体系结构[5]–[14],极性调制已经成为一种很有前途的系统方法。一般来说,在极性调制器中,相位调制(PM)射频载波被放大到所需的功率级,而振幅调制(AM)仅在电路输出阶段重建。在许多极性调制器中,PA本身可以方便地嵌入到调幅过程中[6], [8]–[11]。这样,所有的射频电路(不仅仅是PA)都以恒定的包络方式运行。因此,不需要线性射频放大器。极性调制也有可能从同一终端获得更多操作模式[3], [8]–[14]。

在极性TX体系结构实现中,最经典的是通过改变饱和PA的供应电压来重建振幅调制[6], [8], [10], [11], [14]。根据数字振幅控制字(ACW),可以采用通过适当地打开和关闭大量增益单元的数字调制功率放大器(DPA)作为替代方案。这样一来,因为避免了宽频带的电源管理器,电路更直接地连接到数字基带,模拟电路的复杂性就降低了。

最近,类似的技术已经被用于无线局域网[15], [16]或蜂窝应用[17],以及每个频段仍然需要一个外部PA的低功率电路[18], [19] (10兆瓦的峰值)中。然而,之前提到的DPA只提供了有限的TX功率控制(TCP)能力,这在所有CDMA网络中尤其重要,因为兼容的TX需要高于70 分贝的输出功率范围[20], [21]。在如此高的控制范围内,传统的CDMA PA的平均功耗最终由静止电流控制。

在这一工作中,我们演示了一个多波段的CMOS DPA,用于可重构的极性发射机[22],具有25分贝的POUT。为了满足增益单元的实现,引入了一种新颖的两阶段拓扑结构,能在非常宽的带宽下进行有效的操作。利用自适应数字预失真(DPD)可以实现DPA的线性化,从而实现了高调制精度的EDGE、WCDMA和OFDM信号,达到5 MHz调制带宽。同时提出了一种新的TPC协议,使DPA能够有效地处理典型的CDMA功率控制规范,同时显示低至10毫瓦的静态功耗。

本文组织如下。在第二节中,我们讨论了与数字振幅极性调制器设计有关的系统问题。然后,在第三节中详细描述了装配式DPA电路。最后,第四节讨论了测量结果。

Ⅱ.系统需求

- 系统架构

在极性调制器中,信号被分解为极坐标。通过Vx(t)表示ux(t)的复数包络,根据定义

其中Wc是载波的角频率。这个公式适用于任何带通信号。

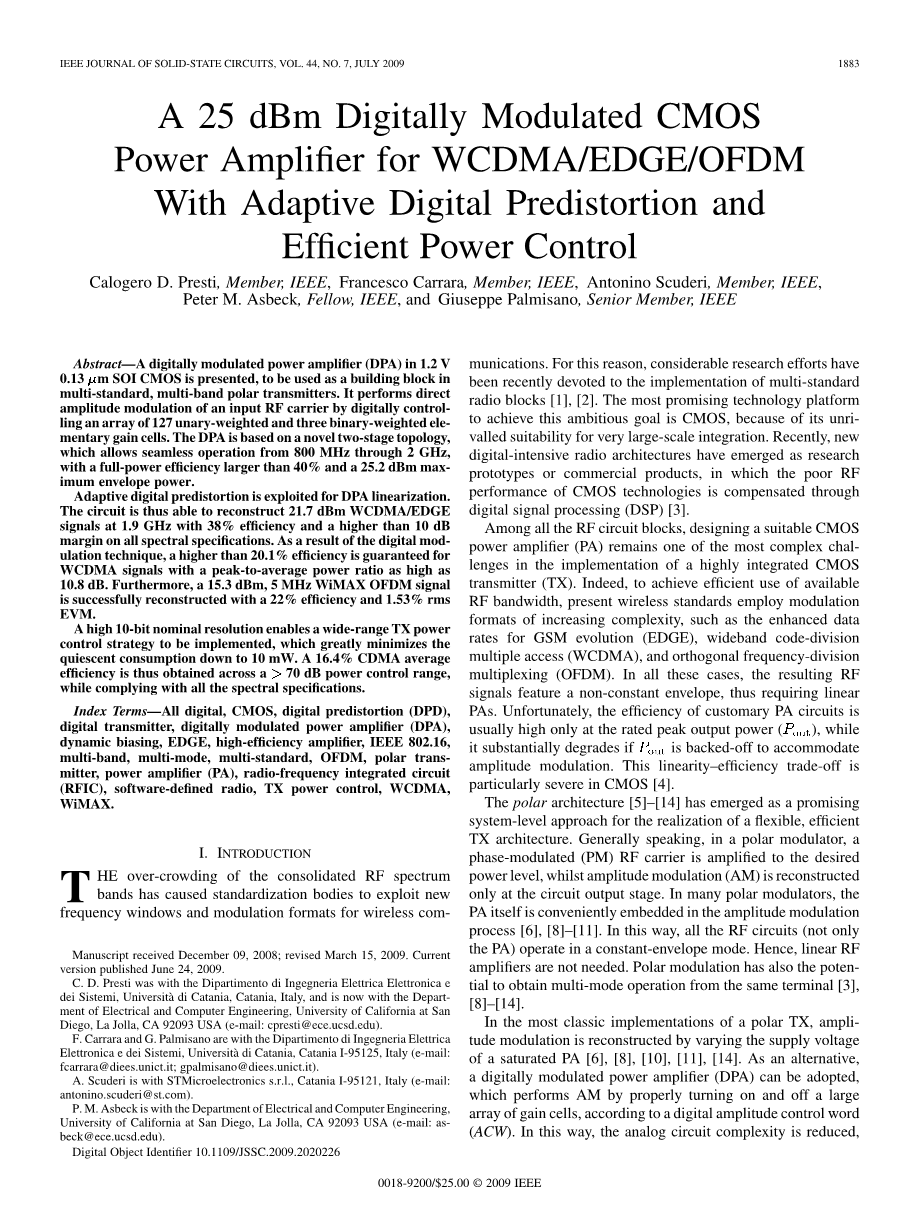

图一 一种大型直接数字射频极性信号发射机的结构示意图

图1中描述了一种方便的基于DPA的极性TX体系结构,其中DPA执行幅度调制。在输入端,基带I和Q信号在数字域中被向上采样,然后转换为极坐标。在早期的极性TX设计中,PM载体和AM组件(1)是通过模拟方式从原始信号ux中得到的,分别通过一个限制器和一个包络检波器[7]。随着近年来TX体系结构的日益数字化,在数字域[3], [15]中可以很容易地进行极性分解。

在极性分解后,相位信息phi;(t)用于调制频率合成器的输出(例如,一个平移回路[7]-[9],一个分式N-PLL[11],或直接调制全数字PLL[3])。PLL输出和带有AM信息的ACW信号分别提供DPA的模拟和数字输入。ACW被用来适当地打开和关闭DPA初级增益单元,从而产生与所期望的ACW样本成比例的输出包络。这样,在TX链中避免了D/A转换器。

B. 非理想因素

众所周知,TX链中性能退化最重要的来源之一是非线性,这导致了AM-TO-AM或AM-TO-PM失真。非线性是光谱再生长和非零误差矢量大小(EVM)的原因。

线性行为意味着DPA输出的射频包络与ACW成正比,输入/输出相移不依赖于ACW:

需要注意的是,在极性TX中,AM和PM信号的分区和重新组合需要非线性操作。因此,即使是线性的非理想性(如延迟或带宽限制)也会严重破坏传输信号。

相对较小的时间偏差导致原始信号频谱两侧的宽带频率分量的出现。这个伪信号实际上是PM载波的宽频谱的一个缩影,因此它可以破坏邻接通道[23]。对于一个双音信号,对AM/PM时间失调的影响进行了理论预测。在这个简单的例子中,给出了三阶互调失真(IM3)。

其中RFBW为射频信号带宽[24]。式(3)可用于粗略估计WCDMA相邻信道功率比(ACPR):

其中K是一个依赖于特定调制参数的经验常数。最大可容许偏差通常等于符号持续时间的一小部分。

除了紧凑的时间校准外,AM和PM路径中的适当处理带宽也必须得到保证,因为两个极性组件的频谱比组合信号的范围更广。定量地说,根据频谱约束的严重程度,可以容忍比RFBW大2到4倍的带宽限制。

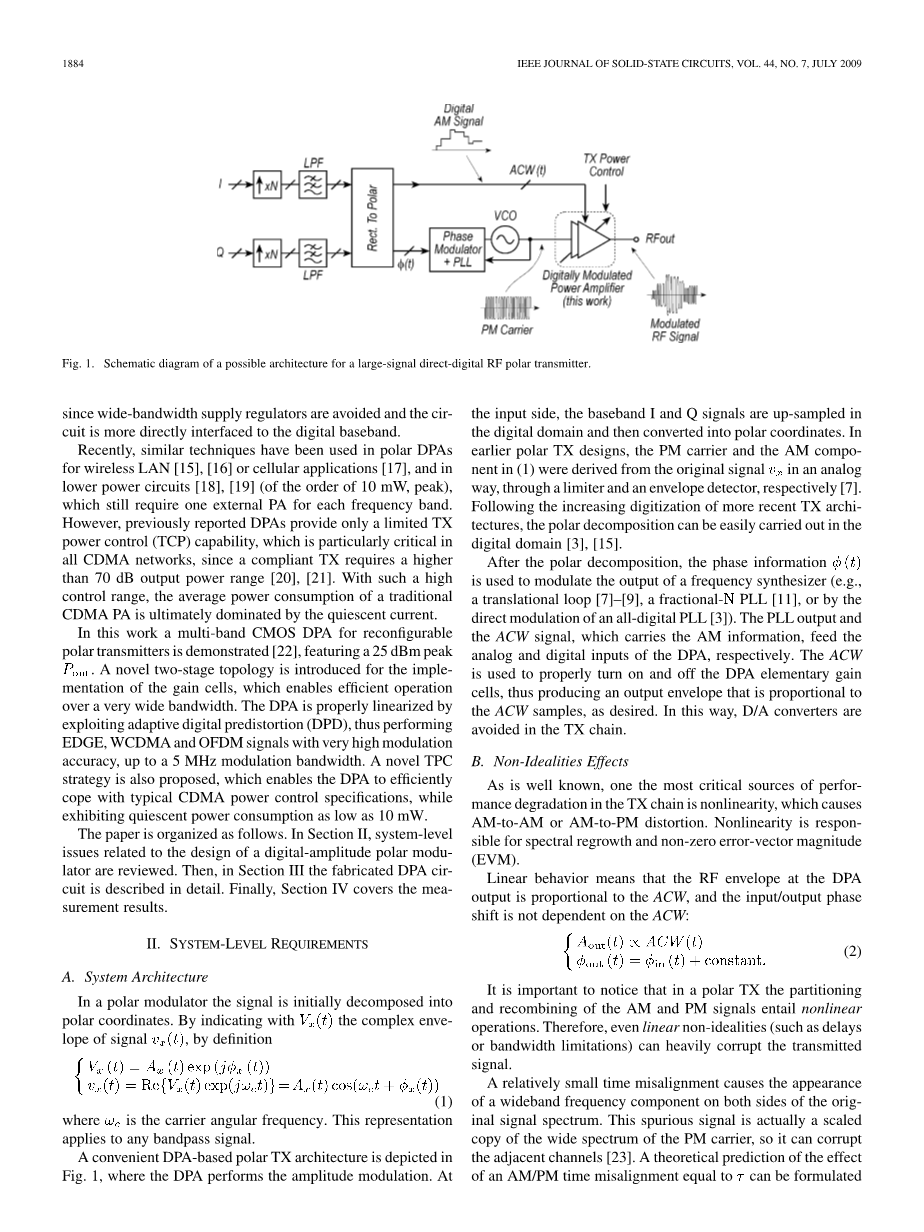

图二 在一个理想的数字-振幅极性调制器的输出中模拟了AM量化对WCDMA ACPR(上)和边缘光谱(下)的模拟效果

对于上述非理想性因素的处理,在图1中采用了数字密集的极性结构与模拟替代方案相比具有以下优点。首先,数字预失真(DPD)可以直接在数字化的体系结构中引入,以纠正调制非线性[3], [11]。其次,在高度集成的系统中,关键的AM/PM时间对齐方式更容易预测,并且可以在数字域中进行校正[25]。此外,AM调制带宽不受任何模拟包络放大器的限制,也不受供给调制的PA解决方案的限制。最后,数字设计对过程电压温度(PVT)的变化不那么敏感,从而提高了调制精度。

在数字振幅极TX中,有限分辨率是一个额外的误差来源。的确,量化误差产生白噪声。作为信号重构的结果,该宽带噪声频谱与PM载波频谱相结合,最终在重构信号的顶部产生白噪声层。通过对理想化的极性发射机进行系统级模拟,得到的光谱再生长函数是AM分辨率的函数。该分析结果在图2中得到了总结,这两种方法均为WCDMA信号,其功率比为3.4 dB /平均功率比(PAPR),采样频率为38.4 MHz,在26 MHz时采样的边缘信号。可以注意到,光谱纯度提高了大约6分贝/位,这是基本的DAC理论预测的。由于噪音是白色的,在5兆赫和10兆赫兹的ACPR是相等的。因此,在10MHz时,更严格的43分贝限制为WCDMA定义了一个最小的6位分辨率,实现了10分贝的实现裕度。另一方面,传统的边缘调制比WCDMA要求更高,因为600 kHz偏移量的伪功率不能超过60分贝。这可以通过使用最小的7位AM分辨率来实现,同时保留10分贝的余量。

Ⅲ.DPA电路实现

- 芯片架构和TX电源控制协议

数字振幅调制器可以通过适当将大量基本增益元件的射频输出电流相加来实现。根据包络大小,数字ACW开启和关闭这些基本单元。

图三 DPA的框图

图四 TX电源控制协议

DPA的框图如图3所示。DPA由PM信号和10位ACW驱动。该方法是一个分段的D/ A转换器[26]:7个最重要的位元(MSBs)由一个双端-温度的解码器处理,以控制127个相同的一元增益单元,而3个最不重要的位(LSBs)控制3个二进制加权单元。这个分段的解决方案是二进制实现的简单性(在没有解码器的地方),和一个一元方法的优越匹配性能(对于这样高的分辨率来说太复杂了)的妥协。双端-温度计解码器是一种自定义数字电路,采用静态CMOS逻辑、数字缓冲器和主从寄存器实现。

除了上述7位要求外,还实现了3个额外的位,原因有两个。首先,ACW到AM失真实际上降低了有效的分辨率,下一节将讨论这个问题。第二,根据图4中所示的协议,可以利用超额分辨率来提高整个WCDMA TPC范围内的系统效率。在高功率下,由于分辨率是冗余的,POUT可以在数字域中减小,即通过逐步扩展ACW,同时保持输入PM信号功率(Pin)常数(数字TPC范围)。当只剩下6位时,由于AM量化误差,ACPR极限几乎达到。因此,进一步的POUT减少只能通过降低Pin (模拟TPC范围)来获得。换句话说,建议的TPC方法首先利用了过量的分辨率,最终降低了Pin。当然,模拟TX的功率可控性要求DPA单元有适当的偏置,因此输出功率也与PM载波功率成正比。

TPC协议的一个主要好处是,低功耗的直流消耗降低了2(10-6)=24。因为所有未使用的单元都关闭了。此外,AM总是通过数字ACW执行。因此,AM不存在于输入PM载体中,因此对射频输入的DPA线性无关(对于输入变增益放大器是相同的)。这有助于减少整个TX系统的功耗。

- 电路细节

DPA的详细示意图如图5所示。射频增益单元的拓扑结构对DPA性能具有重要的意义。特别的是,通过增益单元的频率响应,决定了一个广泛的频率范围,这应该是固有的宽带。所建议的基本单元是一个两级差分放大器。分数单元是一元的复制品。第一个增益阶段(晶体管M1-M4)是一个互补共发射极放大器,其中NMOS晶体管通过C1连接到射频输入。第一阶段是dc-耦合到第二阶段(M5-M6)。该拓扑避免了任何窄带级间匹配网络,从而提供了所需的宽带行为。

每个增益单元的on/off状态由一个enable (EN)信号设置。当EN是高的时候,晶体管M7在三极管区,M8-M12关闭,细胞在上。晶体管M14形成了一个M1-M2 (M13与M7相匹配的M13)的电流镜,而M3-M4则通过M5-M6自偏压并形成了镜像结构。因此,单个单元的两个阶段都可以通过简单地将M7打开/关闭来开启/关闭。

图五 显示基本增益单元的DPA电路原理图

M8-M10增加了非状态隔离,而M11-M12加速放电和改善关闭瞬态。R2-C2网络平滑了驱动单元交换的信号。由此产生的低通滤波作用有助于减少频谱别名,它是由时钟频率fck的倍数的偏移频率产生的。大约这些数字图像的衰减Halias将由一个零阶保持器的经典sin(x)/x响应给出,再加上一阶低通滤波器,其时间常数为R2C2:

其中f是载波的偏移频率。

就线性而言,一个依赖于ACW的输入电容是有害的,因为信号依赖的输入电容在传统的线性PA中。在该方案中,没有断开与输入端的连接,从而大大减少了DPA差分输入电容的变化,仍然等于127·(Cgs1,2 Cgs3,4)/2。在这种情况下,输入阻抗随ACW的变化很小。这减少了ACM到PM失真,通过保持DPA输入的电压波动尽可能稳定,同时ACW是多种多样的。

输出匹配网络(连接线 Lw,差分传输线和Cm)是为了使放大器处于 E类模式,从而优化了饱和的效率。如前所述,在整个模拟TPC范围内,每个单元格都设置了适当的偏置电流以保证适当的操作。

在

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[465739],资料为PDF文档或Word文档,PDF文档可免费转换为Word