英语原文共 12 页,剩余内容已隐藏,支付完成后下载完整资料

采用叠加场效应管结构的毫米波功率放大器的分析与设计

摘要:本文提出了一种新的毫米波叠加场效应管功率放大器设计分析方法,着重研究了通过调整叠层晶体管的复导纳来提高输出功率的问题。分析表明,在给定的场效应管特性下,最大场效应管堆叠数和工作频率存在基本限制。此外,还进行了综合分析,以了解各场效应晶体管参数对限制叠层数和输出功率的影响。在此基础上,提出了一种简单的Cgs补偿设计方法,进一步增加了叠层数,提高了输出功率。为了验证分析,利用PHEMTS和CMOSFET设计并制作了不同频率的各种高频叠加场效应晶体管PAMMIC,它们都具有不同的最大跃迁频率 (fTrsquo;s)。本文综合分析了叠加场效应管放大器在毫米波频段的局限性,提出了一种新的设计方法来进一步提高其在高频段的输出功率性能。

关键词:毫米波集成电路,功率放大器,串联场效应管,叠层场效应管。

一、前言

由于人们对对毫米波功率放大器的兴趣日益浓厚,该放大器用于无线局域网和汽车雷达等新兴商业应用。对毫米波频率下的高效功率合成进行了积极的研究。与传统的分布式交流变压器的并联组合和电压组合的方法相比,采用叠层晶体管的串联功率组合在工作带宽、功率增益和电路尺寸方面具有明显的优势。此外,叠层场效应管结构作为电压合成方法,可以更好地解决低击穿电压晶体管。然而,由于明显的

电抗效应所引起的设计困难,串联组合放大器的实现大多局限于低频的晶体管,导致每个晶体管负载不匹配。与叠层场效应管的低频设计方法不同,毫米波叠层场效应管的最佳负载阻抗是复杂的。此外,在毫米波频段,由于漏源极电容(Cds)的影响,前级部分叠层结构的负载阻抗受到后级 CG-FET 负载阻抗的影响。在毫米波波段,叠层场效应晶体管 PA的一些工作已经发表,并取得了很好的效果。此外,为了获得更高的输出功率,还提出了叠层 PAs 的分析和设计方法。例如,通过在 7GHz的两级 pHEMT 功率放大器中增加外部漏源电容,输出功率得到了改善。通过中间节点与地之间的并联电感加载,三、四叠层 FET 功率放大器获得了较高的输出功率。然而,目前对叠层 FET 功率放大器的分析大多是基于叠层 FET 功率放大器的负载阻抗是纯实值的假设,这可能并不是由于Cds在毫米波频率的显著电抗效应所导致的。在前期工作中,简要讨论了一种基于复杂负载阻抗的毫米波叠层 FET 功率放大器的设计方法,指出了在负载阻抗的Q值和工作带宽增大的情况下,最大 FET 叠层数对于宽带功率放大器应用的实际局限性。

本文发展了一种通用的毫米波叠层场效应管功率放大器设计分析方法,着重研究了通过调整叠层晶体管的复导纳来提高输出功率的方法。分析的基础是计算了具有复杂负载导纳的后继 CG-FET 在堆栈内部节点的输入导纳,使其与前面部分叠层 FET 的最佳负载导纳紧密匹配,以及负载失配对整体输出功率的影响。在第三节中,通过分析可以看出,最大场效应管堆码数和工作频率的自然限制是存在的。文中还提出了一种新的基于方程的 FET 本征参数分析方法,用以解释哪些 FET 参数是限制 FET 堆码数的主导参数。利用所提出的分析,通过对 FET 参数的分析,提出了一种克服输出功率下降的简单方法,其结果见第四节。最后,为了验证所提出的毫米波频率下输出功率衰减补偿方法的有效性和通用性,在第五节中采用 HEMT 和 CMOSFET 设计并制作了不同工作频率和堆叠 FET 个数的堆叠 FET 功率放大器 MMICs。

二、叠层 FET 毫米波功率放大器的分析方法

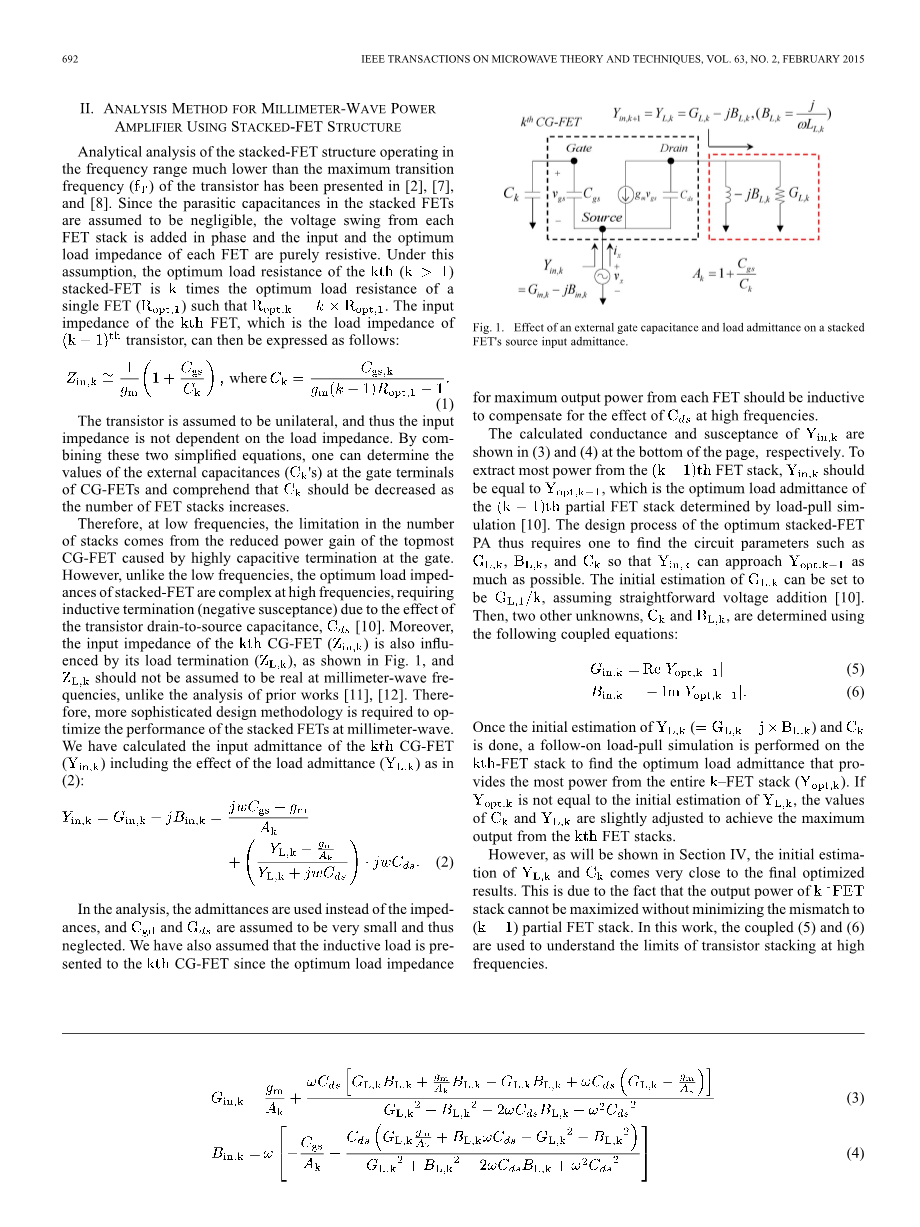

在[2]、[7] 和[8]中给出了在远低于晶体管最大跃迁频率(fT)的频率范围内工作的叠层 FET 结构的分析。由于堆叠式场效应晶体管的寄生电容被假定为可忽略不计,因此来自每个 FET 叠层的电压摆动被相加,并且每个 FET 的输入和最佳负载阻抗是纯电阻的。在此假设下,kth(kgt;1)叠加场效应晶体管的最佳负载电阻等于k与单个 FET(Ropt,1) 的最佳负载电阻的乘积Ropt,k=ktimes;Ropt,1。FET 的输入阻抗,即晶体管的负载阻抗(k-1)th,可表示如下:

假设晶体管是单侧的,因此输入阻抗不依赖于负载阻抗。将这两个简化方程结合起来,就可以确定 CG-FET 栅终端的外电容 (Ckrsquo;s) 值,并理解随着 FET 叠层数的增加,外电容 (Ck) 值应该减小。

图 1. 外部栅极电容和负载导纳对堆叠 FET-s 源输入导纳的影响

因此,在低频下,叠层数目的限制来自于在栅极高电容端引起的最高 CG-FET 功率增益的降低。然而,与低频不同,堆叠 FET 的最佳负载阻抗在高频是复杂的,由于晶体管漏源电容Cds的影响,需要感应终止(负电纳)。而且,CG-FET(Zin,k)的输入阻抗被它的负载终止(ZL,K)影响,如图1所示,并且ZL,K不应该在毫米波频率被假定为真实的,不像以前的工作的分析[11],[12]。因此,需要更复杂的设计方法来优化毫米波堆叠 FET 的性能。我们已经计算了kth CG-FET(Yin,k)的输入导纳,包括正如(2)中负载导纳(YL,K)的影响:

在分析中,用导纳代替阻抗,假设导纳Ggd和Gds很小,因而被忽视。我们还假设感应负载被提供给kth CG-FET,因为最佳负载阻抗对于最大输出功率从每个场效应管感应补偿Cds在高频的影响。

计算得出的电导和Yin,k的电纳分别如 (3) 和 (4) 所示。为了从(k-1)th FET 堆栈中提取最大功率,Yin,k应该等于Yopt,k-1,这是部分(k-1)th FET 堆栈的最佳负载导纳,由负载拉动模拟确定。因此,最佳叠层场效应管功率放大器的设计过程需要找到使Yin,k尽可能接近Yopt,k-1的电路参数,如GL,K,BL,K,和Ck等。假设直接电压增加,初始估计值GL,K可设置为GL,1/k。然后,使用以下耦合方程式确定另外两个未知量Ck和BL,k:

(5)

(6)

完成YL,k(=GL,k-jtimes;BL,k)和Ck的初始估计后,在kth-FET 堆栈上执行后续负载拉动模拟,以找到从整个堆栈提供最大功率的最佳负载导纳k-FET(Yopt,k)。如果Yopt,k不等于初始估计值YL,k,则略微调整Ck和YL,k值以实现 kth FET 堆栈的最大输出。

然而,正如将在第四节中显示的那样,YL,k和Ck的初始估计值非常接近于最终优化结果。这是由于部分 (k-1)FET 堆栈的失配,k-FET堆栈的输出功率不能最大化。在这项工作中,耦合 (5) 和 (6) 是用来了解限制晶体管堆叠在高频。

图 2. (a) (5) 和 (6) 在 20ghz 和 60ghz 的Ck平面上和BL,k在 20ghz 和 60ghz 的平面上的散点图(20ghz时有两种答案,但 60ghz时没有答案) (b) (5) 和 (6) 在最佳负载失配(Bin,k=0.5times;Bopt,k-1)的Ck和BL,k平面上的散点图,使答案在 60ghz 存在。

部分(k-1)堆栈的最佳负载总是由于Cds。然而,从 (4) 可以看出,随着叠层数量和频率的增加,kth CG-FET 呈现的输入阻抗变为电容性(Bin,klt;0);(4) 中唯一的积极影响是

随着叠层场效应晶体管数目的增加和频率的增加,叠层场效应晶体管的数目应该会减少。因此,在高频,Bin,k减少,改变负载阻抗(k-1)部分堆栈从感应电容。这导致(k-1)部分堆栈的负载不匹配。因此,叠加中附加晶体管的功率获益被提供给(k-1)部分叠加的功率不匹配抵消。为了更好地理解功率不匹配问题,在图 2 (a) 中,我们展示了 (5) 和 (6) 在两个不同频率(20 GHz 和 60 GHz)的Ck和BL,k平面上的图。在 60ghz 时,不存在Ck和BL,k同时满足 (5) 和 (6) 的解对。在图 2 (b) 中,引入负载不匹配,直到Ck和BL,k有了解决方案,为此目的将Bin,k其设置为Bopt,k-1一半。为了量化失配引入的功率损失,通过使用(k-1)部分堆栈运行负载牵引模拟生成负载牵引轮廓,如图 3 所示。Bin,k=0.5times;Bopt,k-1产生约 1 dB 的功率失配。如果此功率不匹配大于kth CG-FET 堆栈提供的附加功率,则堆栈数没有超过(k-1)的增加点。

图3.(k-1)th部分场效应管堆栈的负载牵引轮廓线和额外的kth CG-FET 堆栈的最佳负载失配使 (5) 和 (6) 的答案存在

三、采用叠层 FET 结构的毫米波功率放大器的实际局限性

在前面关于内部失配效应的分析的基础上,我们分析了堆叠 FET PAs 的三个关键限制:堆叠 FET 数量、最佳负载阻抗系数和工作频率。

A. 堆栈数目的限制

在理想的电压合成方案中,可以假定叠层放大器的输出功率随 FET 叠层数的增加而单调增加。然而,在实际的高频电路中,这种假设并不总是有效的。这可以通过上一节中介绍的负载不匹配分析进行解释。随着 FET 叠层数的增加,(k-1)th FET(GLoad,k-1=Gin,k)的负载电导应按比例减小以获得最佳的电压合成。这意味着Ck应该随着k增加而减少,如 (1) 所示。Ck越小使Ak(=1 Cgs/Ck)变大。随着堆栈 (k) 数量的增加,Ak越大和GL,k越小的堆栈减少了 (4) 中的主要正贡献GL,kgm/Ak。另一方面,负贡献几乎与增加的k相同。因此,Bin,k变为负值,表示 (k-1)th FET 的电容负载。通过计算表I 中 GaAs mHEMT 在 60 GHz 下的Bin,k,如图 4 所示。

负贡献项:

正贡献项:

图 4.Bin,k中每个贡献项相对于 SNU 0.13 mu;mMHEMT (4times;50mu;m) 的FET叠加数(k)的变化

表一

SNU 0.13mu;m MHEMT、WINFOUNDRY 0.15mu;m PHEMT 和 IBM 0.13mu;m CMOS 的固有参数和负载电导

由于kth FET 电容输入阻抗的失配效应,kth FET 堆的功率增量将小于其理想值10times;log[(k 1)/k]dBm。如果由于负载失配造成的功率损耗大于理想功率增量,则整体堆栈放大器的输出功率将比(k-1)堆栈放大器更小,这有效地限制了堆栈 FET 放大器的数量。图 5 清楚地显示了这种效果,它显示了输入的不同FET 的阻抗和 FET 的最佳负载阻抗。

图 5.随着场效应管堆叠数的增加,(k-1)th FET的最佳负载导纳和kth FET输入导纳之间的失配程度

此外,堆栈数多,负载因子高。随着叠层数的增加,GL,k应按比例减小到G1/k电压相加。相反,BL,k应该增加以最小化对(k-1)th FET 的不匹配效应,因为 (4) 中的正项omega;CdsBL,k应该最大化。这导致在毫米波频率下负载(Q=BL,k/GL,k)的系数更高,从而如[10]所述,限制了毫米波叠层 FET 放大器的工作带宽。这种效应不能从低频分析中解释,低频分析没有考虑反应性效应。

B. 工作频率限制

堆栈数量的限制表现在不同的方面,这取决于工作频率。为了更好地量化这一点,在 20 到 60 GHz 的不同频率下分析了使用 0.15mu;m pHEMT 实现的双层 FET 放大器(共源共栅放大器)。FET 采用的单元晶体管为 4times;50mu;m,等效电路参数列于表I,对于共源共栅放大器,底部 FET (CS-FET) 的最佳负载电导(BLoad,k)为omega;Cds。因此,(4) 可表示为 (9):

lt;

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[608994],资料为PDF文档或Word文档,PDF文档可免费转换为Word