英语原文共 8 页,剩余内容已隐藏,支付完成后下载完整资料

用于全球卫星导航系统接收机的低相位噪声和低杂散PLL频率合成器

李森,江金光,周细凤,刘江华

1School of Physics and Technology, Wuhan University, Wuhan 430072, China

2GNSS Research Center, Wuhan University, Wuhan 430072, China

3Suzhou Institute, Wuhan University, Suzhou 215123, China

摘要:本文提出了一种用于全球导航卫星系统(GNSS)接收机的低相位噪声和低杂散锁相环(PLL)频率合成器。为了得到一个较低的杂散,对称结构的相位频率检测器(PFD)将会产生四个控制信号,它们可以同时到达电荷泵(CP),并且可以改善的CP,从而以达到最小化电荷共享和电荷注入,使电流匹配。此外,由于PFD为可编程的器件,所以延迟是可控制的,因此可以消除CP的死区。压控振荡器的输出频率可以通过使用一个可编程LC-TANK连续且精确地调整。使用适当尺寸的MOS可使得VCO的相位噪声更低。本文所提到的锁相环频率合成器是由0.18mu;m的混合信号CMOS制作工艺制成。在频率为1MHz时测量的相位噪声距离中心频率的偏移量为-127.65dB/Hz,参考杂散为–73.58 dBc.

关键词:PLL频率合成器; 相位噪声; 杂散 鉴相器; 电荷泵;压控振荡器

DOI: 10.1088/1674-4926/35/1/015004 EEACC: 2570

1.简介

GNSS接收机,便携式数字视频广播设备和通信系统在现代社会中起着重要的作用。PLL频率合成器是这些设备的关键部分,其性能和作用对系统的性能有很大的影响。杂散和相位噪声是PLL频率合成器的两个关键性能指标。因此,具有低相位噪声和低杂散的PLL频率合成器的设计和实现对于设计者来说是一项具有挑战性和较为困难的任务。

为了实现PLL频率合成器的低相位噪声和低噪声,人们已经提出了许多方法。然而,这些方法无法避免相位噪声和杂散之间的设计矛盾。更为重要的是,电路结构理解起来较为困难而且实现比较复杂。为了减少非理想因素和提高性能,本文重点介绍了PLL频率合成器的新架构。本文设计了一种新颖的频率相位检测器用于提供四个控制信号并消除死区。 电荷泵是以一种新的方式进行实现,从而获得匹配的电流,而且为了得到更低的杂散值将电荷分享和电荷注入降为最小。通过使用可编程块,压控振荡器的输出频率可以连续且精准地进行调节。另一方面,由于使用适当尺寸的MOS,压控振荡器具有低相位噪声。

本文的其余部分组织如下:第2节介绍了锁相环频率合成器的结构。第3节中介绍频率合成器的所有块的电路细节设计。然后,第4节介绍了仿真和测量结果。最后,第5节给出所得结论。

2.PLL频率合成器的结构

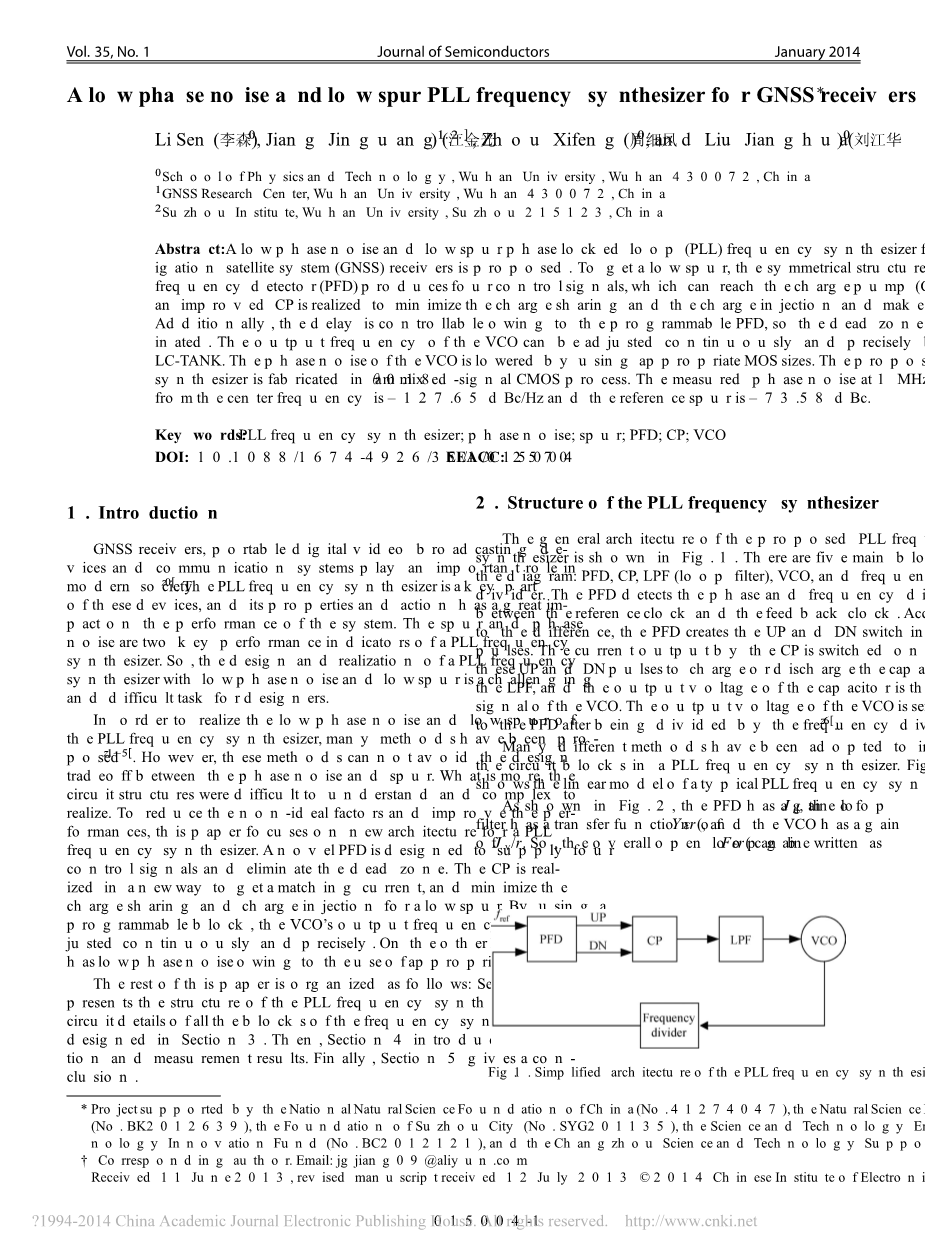

所提出的PLL频率合成器的一般架构如图1所示。图中有五个主要模块:鉴频鉴相器,电荷泵,LPF(环路滤波器),压控振荡器VOC和分频器。 PFD检测参考时钟和反馈时钟之间的相位和频率差。依据检测差值,PFD产生UP和DN转换脉冲。 电荷泵的电流输出由这些UP和DN脉冲接通或关断,从而对低通滤波器中的电容器充电或放电,电容器的输出电压是VCO的控制信号。由分频器分频后,VCO的输出电压被送回PFD。

许多种不同的方法被用来实现PLL频率合成器中的电路模块。图2显示了典型PLL频率合成器的线性模型。

如图2所示,PFD的增益为Kd,环路滤波器具有Z(s)的传递函数,VCO的增益为Kv/s。所以,整体开环增益G(s)可以写成:

在本文中,参考信号fref由频率为16.386MHz的片外晶体振荡器产生。为了减小芯片的面积,LPF在片外部件中实现。分频器的分频比为96。

3.电路细节描述

3.1 鉴频鉴相器和电荷泵中的非理想效果

在实际的电路中,MOS开关等部件产生电荷注入,电荷共享等。 那些非理想行为引起参考杂散,近似可写为:

其中N是分频器的分频率。 fbw是环路带宽,fpl是环路滤波器的极点频率。是相位误差,可写为:

其中Icp是电荷泵的输出电流。Ileakage是漏电流。 Tref是参考循环时间。 Ton是PFD的开启时间。 Ai和Atdelay分别是失调电流和时间差。

公式(2)表明,通过降低Ad,fbw或fref可以减少杂散。在本文中,仅Ad是需要被进行处理的。

方程式(3)中的Ileakage可以忽略,因为Ileakage lt;lt;Icp。 Tref由片外晶体振荡器所决定。因此,可以通过最小化ton,Delta;omega;,Delta;tdelay和选择适当的Icp以减少刺激来实现最佳的。

和是电荷泵里的不理想因素,然而和是相位频率监测器的不完全效果。因此本文首先描述了PFD。

3.2 鉴频鉴相器

鉴频鉴相器可以快速有效地检测两个输入信号的相位差。电路结构如图3所示。边缘触发的D型触发器(DFF)具有真正的信号相位时钟(TSPC)结构,其由比其他类型的DFF更少的晶体管组成,以减少芯片面积。 另外,它没有静态功耗,动态功耗也相当低。

3.2.1 优化 tdelay

为了减少Delta;tdelay,在图3中提出了完全对称的结构。 虚线内的电路是两个相位非重叠的时钟。 由于使用XOR2(XOR3)作为传输门,并且具有与XOR1(XOR4)完全一致的结构,因此信号可以同时达到NAND1和NAND2(NAND3和NAND4)。因此,被优化到可以忽略的等级。

3.2.2 优化 ton

在确保CP可以在小的相位差下切换以避免死区的条件下,T应该尽可能的小。所以T是在Delta;fai和死区之间的一个权衡。

如图4所示。 如图4所示,Q1-Q8是确定延迟时间的控制开关。 Q9-Q16是相同的MOS电容器。如表1所示,通过改变控制信号Delaylt;1gt;Delaylt;0gt;可以获得四种延迟时间信号。因此,可以选择适当的ton来折算Delta;fai和死区。

3.3 电荷泵

Icp在a 和功率耗散之间有一个权衡。此外,Delta;i是由电流不匹配,电荷泵的电荷共享电荷注入所造成的。因此在设计电荷泵的过程中这三个关键需要考虑在内。

如图5(a)所示,该电荷泵包含三个部分:一个偏置电流,一个泵上和泵下电路、一个可控制的泵上和泵下电路。滤波器用于将Icp改变为VCO的输入电压。控制信号为在图5(b)所示的。

偏置电流采用基本级联结构来保证电流匹配。为了降低结构产生的大噪声,由Mp3-Mn6构成的MOS电容器连接到偏置电流的输出端子分别。当电流流过它们时,混合在其中的噪声可以被过滤。

在泵进和泵出电路中,Mp5 (Mn7) 是一个开关。与常规结构相比,不同之处在于添加了由Mp7-Mn10组成的MOS电容器。如果不使用这些电容,当Mp5关闭时,由于Mp5的源极 - 漏极寄生电容,Mp5的漏极端子电压将上拉至VDD,从而导致电荷共享。通过将Mp7的一端连接到Mp5的漏极,另一端连接到UP,Mp5和电容Mp7的寄生电容串联在VDD和UP之间。因此,漏极电压被钳位在比VDD低的电压值处,以减少电荷共享。此外,当开关断开时,电容器可以快速消耗部分通道电荷,以解决电荷注入的问题。通过将Mp8连接在VDD和UP之间,可以进一步抑制杂散和噪声。泵送的两个部分具有相同的工作原理。

由于开关被加入的信号Cp lt;0gt;和Cp lt;1gt;控制,所以可控的泵进和泵出电路是可编程的。然而,Mp11和Mn15必须在一个周期内打开和关闭一次,导致电荷共享和电荷注入。 为了解决这个问题,使用Mp10和Mn11。通过改变信号Cp lt;0gt;和Cp lt;1gt;选择工作支路,通过设置Mp12和Mn13的W/L来决定每个分支的电流。在本文中,电流源I1,I2,I3和I4分别为20mu;A,100mu;A,400mu;A,200mu;A和100mu;A。因此总共有四种Icp,如表2所示。

环路滤波器可将电荷泵的输出电流转换为压控振荡器的输入电压。 R1与C2串联放置以稳定零点。 添加C1以减少纹波。

从上述分析可以看出,鉴频鉴相器和电荷泵的新结构可以有效地降低刺激。低相位噪声主要出现在压控振荡器的设计中。

3.4 压控振荡器

为了减少相噪声,大多数报告的技术都集中在使用大量组件的新结构上。然而,更多的组件可能会导致更大的区域和更复杂的结构。因此,本文试图改变设备的尺寸,以减少相位噪声。如参考文献[10]中的插图,特征频率ft和栅极驱动Vgs-Vt可以分别由方程式 (4)和(5)来进行表示。

我们可以看出当W减少时,ft和Vgs-Vt都会增加。而相位噪声与ft和Vgs– Vs成反比,因此,可以推导出当W较小时,相位噪声减小。将NMOS的宽度从200减少到10mu;m大约可以讲整体的相位噪声减少20dB。此外,还需要NMOS的大的漏极电流来降低相位噪声。压控振荡器采用的方案如图6所示。它包含四个部分:一个负阻电路、一个LC-TANK,电流偏置电路和缓冲电路。LC-TANK的详细示意图如虚线所示。

采用具有小W / L的一对交叉耦合MOS晶体管(MP1,MP2,MN1和MN2)作为负电阻来补偿LC-TANK中的损耗。 LC-TANK包括中心抽头电感器L1,由PMOS变容二极管VC1和VC2组成的CVAR1,以及由4位开关控制的电容器阵列CCAR4(C1-C4)。 LC谐振频率可表示为:

其中L1是固定的,其中CPARA是系统的杂散电容.CX是电容器阵列的每个分支的总电容。 因此,通过LC-TANK中的开关电容器阵列(C1-C4)实现粗略的频率控制。 另外,VC1和VC2可以使频率精确而连续地进行调谐。

为了降低功耗,可以在VDD与MP6的栅极之间加上K0,它可以在静止状态下使VCO关闭。 K [3:1]被应用到图6中的MP7-MP9的门。 可以通过改变K [3:1]来获得VCO的各种核心电流。 因此,可以改变VCO的输出电压幅度。 此外,由于PVT(工艺,电压和温度)的变化引起的相位噪声和频率偏差的恶化可以最小化。所有开关K [7:0]都由具有较大W / L比率的PMOS实现,以减少相位噪声。此外,为了降低VCO的噪声,添加C5和C6以滤除PMOS晶体管和电源的噪声。

3.5 其他组件模块

如图7所给出的,分频器的的分频比是96。它包含一个高速2分频和一个三分频分频器,四个异步二分频分频器。如图8所示,高速分频器由电流模式逻辑(CML)结构实现。由于CML结构包括固定的尾电流源和较小的输入和输出摆幅,它更适合高频应用程序。此外,由于它的其差分结构,噪声可能比单端更低。

4. PLL频率合成器的仿真和测量

所提到的PLL频率合成器是采用0.18mu;m混合信号CMOS工艺制造,并使用1.8V电源进行供电。芯片的总面积大约是1.2*0.9平方毫米。图9显示了PLL频率合成器的显微照片。通过使用Cadence Spectre进行模拟,并使用RSA3408A频谱分析仪进行测量。在正常的工作环境下,使用1.8V电源进行供电,压控振荡器和分频器分别消耗2.3 mA和1 mA。锁相环频率合成器其他部分在1.8 V电源供电下消耗约0.7 mA。所以PLL频率合成器的总功率大约是7.2兆瓦。

首先,在图10中显示了PFD的仿真特性,从图10(a)和10(b)中可以看出, 信号UP和DN同时以205ns到达CP,所以Atdelay几乎是零。

图11(a)显示了两个单位延迟的模拟延迟时间,图11(b)比图11(a)放大了大约200ns。从图11(b)和10(b)中可以看出,ton可以调整的范围为1〜5ns,并且每个单位延迟约为0.6ns。

其次,在图12中显示了电荷泵和LPF的模拟特性。第二节的充电开关和放电开关都打开。注意滤波器的输出电压是一个平坦的线,这表明充电电流等于放电电流,所以Ai大约是零。此外,第1节的充电过程和第3节的放电过程的斜率都是常数。这一事实说明了电荷泵具有良好的匹配特征并且非理想因素对电荷泵几乎没有影响。

然后,VCO的模拟输出结果的1/2如图13所示。我们可以注意到1.45-1.63 GHz频段在曲线的线性区域,线性区域的斜率不是很大。由于Kv值比较小所以相位噪声较低。锁相环频率合成器主要为GNSS L1频段设计,所以频段满足该需求的范围。

最后,图14显示了在1.571 GHz处于锁定状态的输出信号的测量光谱。图15(a)表明,中心频率为1.571 GHz,当偏离中心频率1 MHz时测得的相位噪声为-127.65 dBc / Hz。图15(b)表明,距离中心频率偏移1 MHz的模拟相位噪声为-129.32 dBc / Hz。它们之间的差异主要是由电容器的寄生效应,过程和温度的变化引起的。图16显示了PLL频率合成器的输出信号的测量结果。

所有这些仿真和测量结果

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[137802],资料为PDF文档或Word文档,PDF文档可免费转换为Word