英语原文共 3 页,剩余内容已隐藏,支付完成后下载完整资料

将高纯度X波段信号倍频至W波段的有源GaAs倍频单片的设计与实现

Palomba,M. , Colangli,S. , Ciccognani,W. , Limiti,E.

一、简介

随着毫米波在雷达、天文学、安全和防御系统等领域的应用越来越广泛,人们对W波段毫米波的研究兴趣也逐渐浓厚。目前,如何直接获得稳定的W波段信号仍是一个研究难点,所以现在研究人员经常采用的方案是采用倍频器(FM)来间接获得该频段的信号,原理是利用倍频器将廉价并稳定的低频信号转换为所需的高频信号。本文所涉及的调频系统主要可以应用于频率合成器和通信电路。

倍频器的主要原理是利用无源器件和有源器件的非线性特性来实现频率的倍增。倍频器的一种工作原理是使用非线性传输线,提供12.8 dBm的输出功率,输出频率范围为81-108.8 GHz,驱动功率为24 dBm。另一种则是利用二极管作为非线性元件,由于二极管是无源器件,因此基于二极管制造的倍频器是有损耗的。这就导致了虽然基于变容二极管的柔性制造系统可以达到理论上的100%效率,但实际上只可以实现的1/x效率。电阻二极管的情况更糟,通常只能达到1/x^2倍频效率。

另一方面,利用场效应管的有源倍频器在工作带宽和转换损耗方面有着很好的性能。目前已有文献报道了一种采用场效应管来实现times;8和times;12倍频器的毫米波系统。前者输出功率为6.9dBm,谐波抑制为13dBc,后者输出功率为1.5dBm,谐波抑制为12dBc。另有报告使用相同技术实现的另一个times;12 倍频器。它由级联times;2-times;3-times;2 的倍频器组成,输出功率为-0.8dbm,转换增益为0.2dB,抑制不需要的谐波为25.5dBc。本文提出了一种有源高次谐波抑制times;8倍频器设计,并给出了相应的设计方法。

二、倍频放大器

如前所述,产生W波段信号的一种有效方法是采用一个容易获得X波段信号的信号源,然后倍频至所需要的高频段信号。鉴于频率分配和结果方案的通用性,选择了一个times;8倍频器作为解决方案,该倍频器的实现有以下几种方法:第一种方法是直接乘法(times;8单次倍频),然而这种方法意味着转换效率会非常低,必须通过插入大量增益级来平衡,以补偿由此产生的信号损失;另一种方法是通过级联低次倍频器来实现所需的乘法因子。考虑到times;8目标的实现,可以考虑三种情况:times;2-times;2 times;2、times;2-times;4或times;4-times;2。前者是复杂的,并导致结构十分复杂,而times;2-times;4和times;4-times;2之间的差异很小,主要优点表现在电路紧凑性和易于谐波控制。再考虑到芯片面积需要尽可能的小,那么times;4 -times;2的方式是首选的。

为了实现调频,选择了单片OMMIC D01MH工艺,在砷化镓基板上提供具有0.13微米栅极长度的耗尽模式MHEMT。铸造库中的无源等效电路模型保证高达25GHz,因此需要大量使用电磁模拟。而一旦定义了乘法块的顺序,就必须引入最终的增益级,以获得所需的总功率性能。然而,这些选择可能受到最大有源设备功率处理能力的制约。

倍频器的结构如图1所示。它由连接到输入端口的times;4调频、缓冲级、times;2调频和最终放大级组成,以提供所需的增益和功率级。Q波段的缓冲级作为一个简单的增益放大器,也用来分离两个调频系统。这样的分离可以减少由于各个倍频器之间谐波的相互作用而产生的误差。因此,缓冲阶段实际上控制着每个需要的或不需要的谐波。

图1 times;8倍频器结构图

图2 times;4倍频器结构图

图3 用于times;4倍频器的4times;55mu;m FET的电流谐波与Vgs

times;4倍频器的结构如图2所示,在偏压有源器件的输入(IMN)和输出(OMN)上有两个匹配网络。前者匹配输入中心频率的输入,后者匹配相同参考频率的第四谐波。偏压线上的四分之一波传输线实际上为四次谐波提供了开路,同时适当地加载了低阶谐波。为了偏压和调整FET的尺寸,可以使用上文讨论的设计图表。经过仿真可以得到结果如图3,其中所选场效应晶体管(4times;55mu;m)的漏极端的电流谐波偏向于VDD=2.7V,作为VGS的函数。黑色曲线代表4次谐波,红色虚线代表5次谐波,以及低阶谐波。考虑到VGS=-0.85V,第5次电流谐波结果的最小值。为了抑制基波、二次谐波和三次谐波的贡献,采用了集总五阶高通滤波器。其结构如图4所示。

图4 times;2倍频器结构图

三、结论

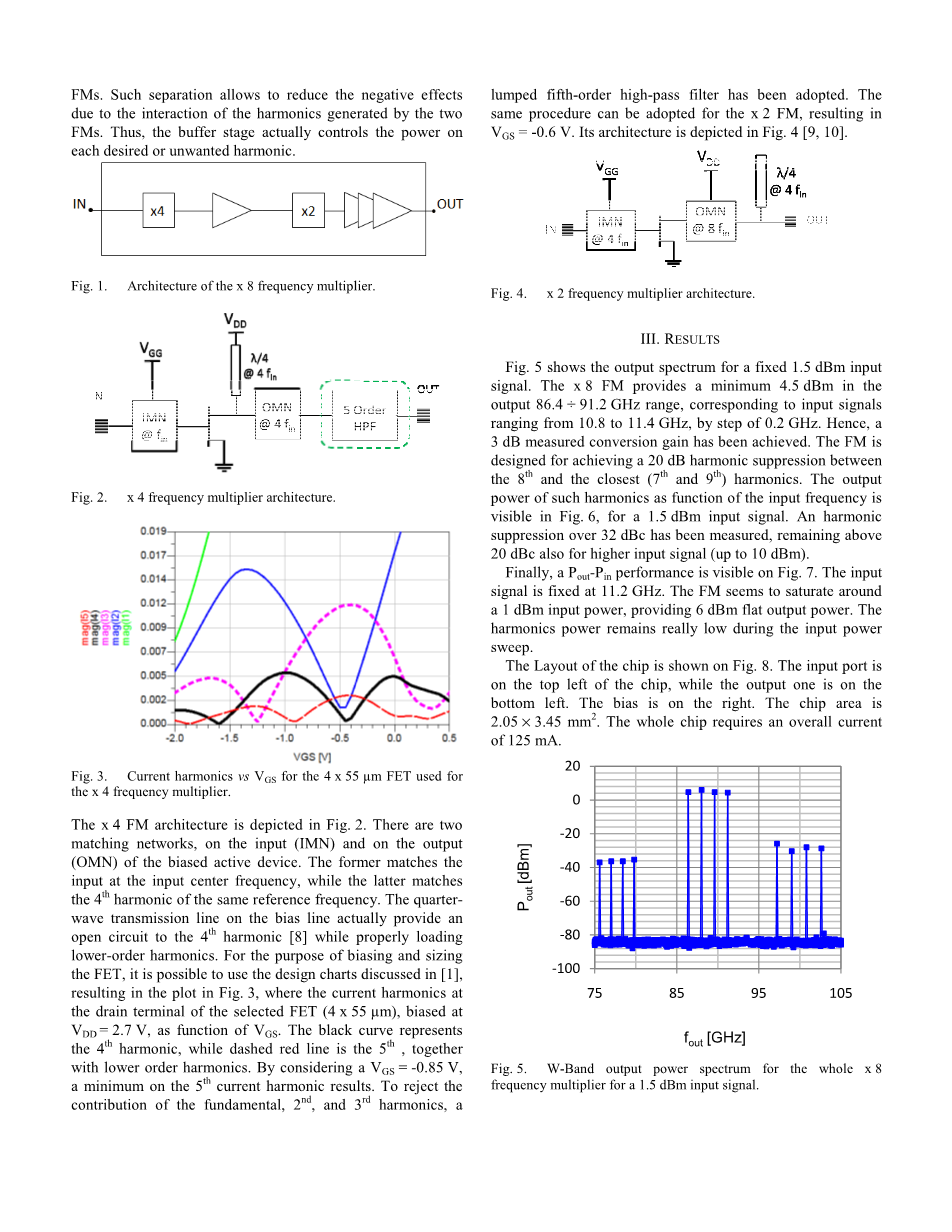

图5显示了固定1.5 dBm输入信号的输出频谱。times;8 倍频器在输出86.4-91.2 GHz范围内提供最小4.5 dBm的输出功率,对应于从10.8-11.4 GHz的输入频率,幅度为0.2 GHz。至此,已经实现了一个3dB的转换增益。倍频器设计用于在GT和最近的谐波之间实现20dB的谐波抑制。对于1.5 dBm的输入信号,谐波的输出功率如图6所示。可以观察到超过32 dBc的谐波抑制,对于更高功率的输入信号(最高为10 dBm),谐波抑制仍高于20 dBc。

最后,图7显示了PAUR管脚的性能。输入信号固定在11.2 GHz。在输入功率扫描过程中,如果6 dBm的平坦输出P谐波功率仍然很低,那么倍频器近似在1 dBm的输入功率周围饱和。

芯片的布局如图8所示。输入端口在芯片的左上角,而输出端口在左下角,偏压在右上角。切屑面积为2.05times;3.45 mm。整个芯片需要125毫安的总电流。

图5 1.5 dBm输入信号的整个times;8倍频器的W波段输出功率图

图6 第7、第8和第9输出功率谐波,作为1.5 dBm输入信号的输入频率图。

图7 第7、第8和第9输出功率谐波,作为11.2 GHz输入信号的输入功率图

图8 times;8倍频器的布局。切屑尺寸为2.05times;3.45 mm

四、总结

本文提出了一种高次谐波抑制有源X波段到W波段调频的方法。给出了设计过程和所得到的仿真结果,得到了一个times;4-times;2的八次倍频器,并给出了该倍频器的设计流程。测量结果表明,该倍频器在W波段的转换增益为3dB,并且所需的第8次谐波和其余不需要的谐波之间的谐波抑制超过32 dBc。 该电路在输入功率为1 dBm时开始工作,最高可达10 dBm。

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[20217],资料为PDF文档或Word文档,PDF文档可免费转换为Word