英语原文共 4 页,剩余内容已隐藏,支付完成后下载完整资料

基于LDO的无电容,具有快速瞬态响应特性的高转换率误差放大器

克里斯蒂安拉杜坎马吕斯Neag

克卢日 - 纳波卡,28圣备忘录,克卢日 - 纳波卡,罗马尼亚理工大学

电子邮件:marius.neag@bel.utcluj.ro

摘要:本文提出了一种高转换率的错误放大器(EA)用于实现一个具有非常快速的瞬态响应的无电容低压差电压稳压器(LDO)。该建议提高EA最近公布的OA结构,由采用高摆幅输入缓冲器和当地的共模反馈。因此,有关EA gainbandwidth和转换率的数字品质因数是2.75,更好分别为24倍比初始的OA。该EA被用来实现LDO仅需要1.1uA静态电流,但有一个输出为100mA电流能力。 EA的高转换率有助于该LDO实现低过冲/下冲(200mV的/ 274mV)在快速(1微秒)负载为100mA步的情况下,只有采用100pF的一个芯片上负载电容。与同类相比实现方式中,所提出的LDO产量相同或更好的同时要求显著少的瞬态性能静态电流。因此,它的品质因数导致至少三比其同行更美好的时代。的线路和负载调控是0.07mV / V,分别0.0028mV /毫安。

关键词:高转换率;误差放大器;我愿意;

1 引言

该低压差稳压器(LDO)是一个线性稳压稳压器,采用PNP或PMOS旁路晶体管作为控制元件,即使当稳定输出电压电源和输出之间的电压差下降到相对低的值 - 下降到几百毫伏。

一个典型的LDO采用一个外部去耦电容既作为快速负载瞬变和频率的能量槽赔偿。然而,在系统级芯片的情况下(SoC)的设计这种方法需要大量的管脚,这并不总是可接受的。因此,研究在过去的多年来一直专注于方法来消除外部输出电容而不影响瞬态性能。

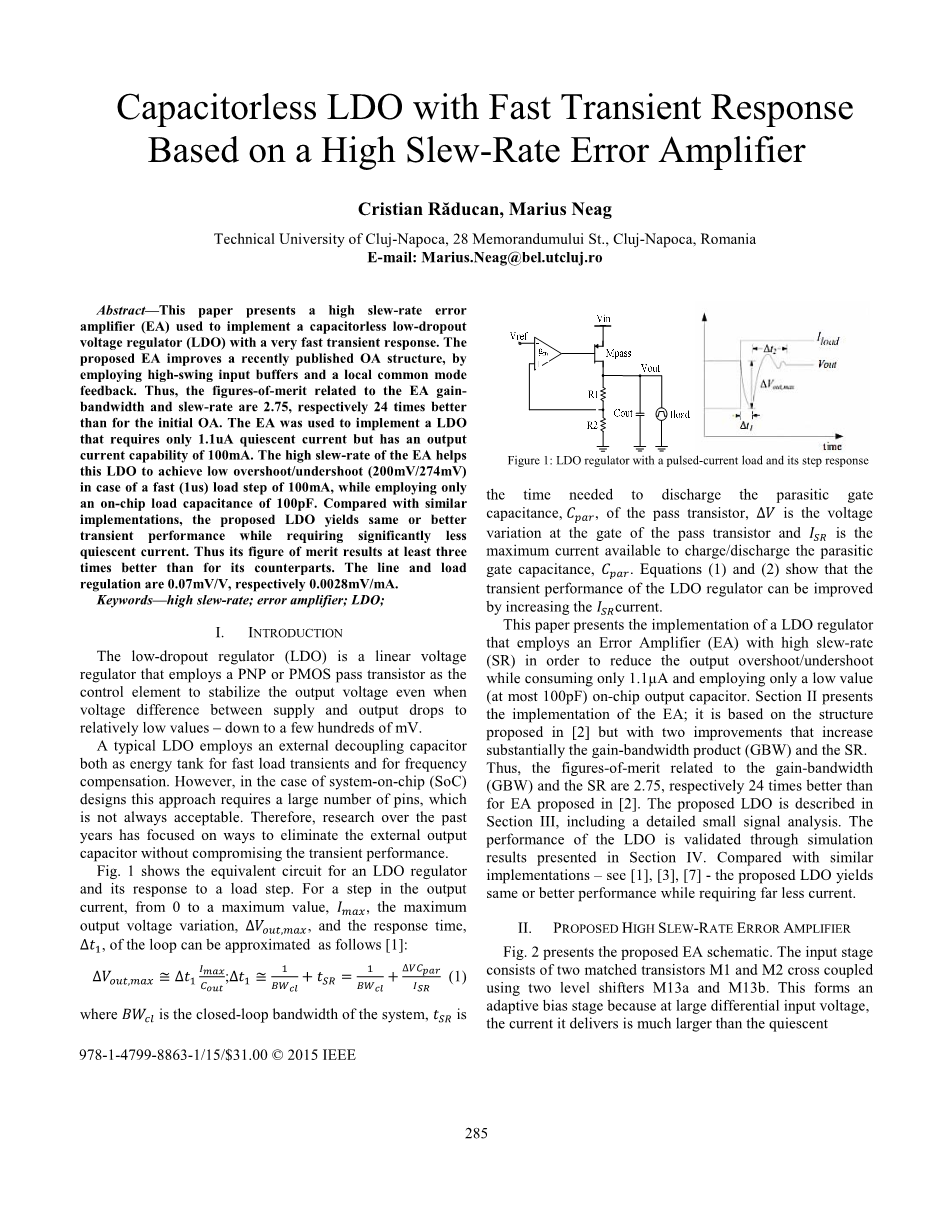

图。1示出了用于将LDO稳压器的等效电路和其对负载阶跃响应。在输出步骤当前,从0到最大值最大的输出电压的变化,和响应时间。环路可近似如下【1】:

[1]

图1:LDO稳压器利用脉冲电流负载和其阶跃响应

其中,是该系统的闭环带宽,是寄生栅极电容来放电所需的时间,是在传输晶体管的栅极变异电压和是提供给充电/放电的寄生电容的最大电流,式(1)和(2)表明,通过增加电流可以改善该LDO稳压器的瞬态性能。

本文提出了一种LDO稳压器的实现,它采用高转换率(SR)误差放大器(EA)以减少输出过冲/下冲而只有1.1mu;A消耗和只采用一个较低的值(最多100 pF)的片上输出电容器。第二节讲述了EA的执行情况;它是基于结构在[2],但具有两个改进,增加提出基本上增益带宽积(GBW)和SR。因此,图中的品质因数相关的增益带宽(GBW)和SR是2.75,分别优于[2]中提出的(EA)24倍。在第三节则描述了LDO建议,包括详细的小信号分析。该LDO的性能是通过仿真验证结果第四节介绍。与同类相比实现 - 见[1],[3],[7] - 所提出的LDO产量相同或更好的性能,同时要求远不如当前。

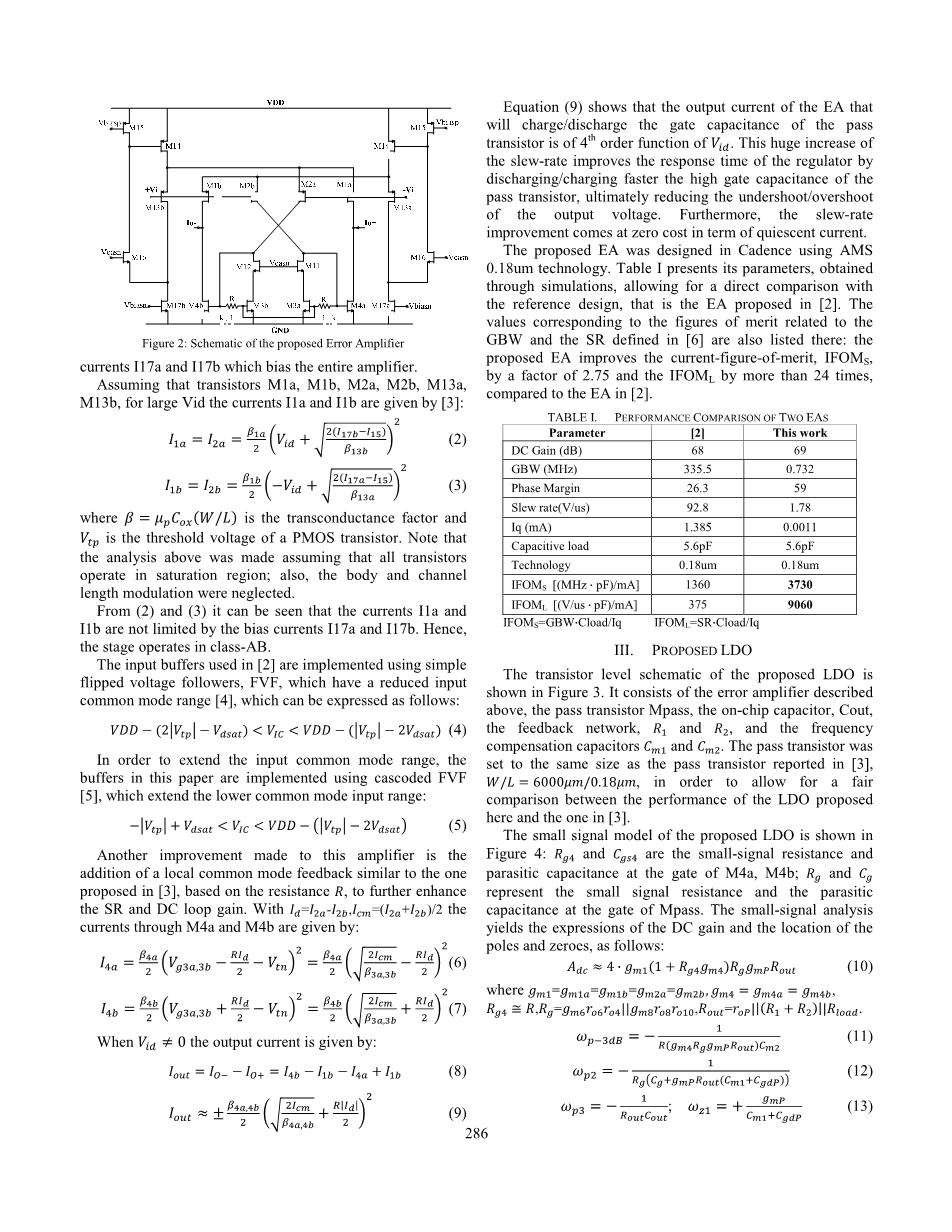

2 拟议的高转换率误差放大器

图.2介绍了拟议的EA示意图。输入级由两个匹配的晶体管M1和M2的交叉耦合使用两个电平转换器M13a和M13b。这形成一个因为大的差分输入电压自适应偏置阶段,它提供的电流比静态大得多。

图2:所提出的误差放大器示意图

电流I17a和I17b偏置其整个放大器。假设晶体管的M1a,M1b,M2a,M2b,M13a,M13b,型对于大的Vid的电流I1a,I1B由[3]给出:

(2)

(3)

其中,是跨导因子,是PMOS晶体管的阈值电压。注意上面的分析,假设所有晶体管工作在饱和区,也就是主体和信道长度调制被忽视。

从(2)和(3)可以看出,该电流I1a与I1B不受偏置电流I17a和I17b限制。因此,

该放大器工作在AB类。

在[2]中使用的输入缓冲器实现简单翻转电压跟随,这具有减小输入共模范围[4],这可以如下表示:

(4)

为了延长所述输入共模范围,本文缓冲区使用共源共栅FVF实施,如[5],它延伸到下端的共模输入范围:

(5)

该放大器提出的另一项改进是另外的一个本地共模反馈一个类似于[3],基于电阻R以进一步提高提出的SR和DC环路增益。与,通过M4A和M4B电流由下式给出:

(6)

(7)当时,输出电流由下式给出:

(8)

(9)

式(9)表明,EA的输出电流将充电/放电合格的栅极电容晶体管4阶的功能。这种巨大的增长摆率提高了调节器的响应时间放电/充电速度更快的高栅极电容旁路晶体管,最终降低下冲/过冲的输出电压。此外,摆率提高是在静态电流的长期零成本。

EA建议的目的是在使用Cadence的AMS0.18微米技术。表Ⅰ给出其参数,获得通过模拟,允许与直接比较参考设计,也就是EA[2]中提出。该对应于功的相关的数字值GBW和[6]中还列出有限定的SR:所述建议EA提高电流的数字品质因数,相比于EA[2],IFOMS由2.75倍,超过24倍IFOML。

表一 两EAS的性能比较

|

参数 |

【2】 |

该EA |

|

直流增益(分贝) |

68 |

69 |

|

GBW(兆赫兹) |

335.5 |

0.732 |

|

相位裕度 |

26.3 |

59 |

|

压摆率(V/us) |

92.8 |

1.78 |

|

电流(mA) |

1.385 |

0.0011 |

|

负载电容 |

5.6pF |

5.6pF |

|

工艺 |

0.18um |

0.18um |

|

IFOMS[(兆赫·pF)/mA] |

1360 |

3730 |

|

IFOML[(V/ us·PF)/mA] |

375 |

9060 |

- 拟议的LDO

建议LDO的晶体管级原理图如图3所示它由如上所述的误差放大器,通过晶体管MPASS,芯片上的电容COUT反馈网络,R1,R2,频率补偿电容,传输晶体管设置为相同大小如[3]报导的传输晶体管,为了允许公平LDO的建议之间的性能对比这里和一个在[3]

所提出的LDO的小信号模型如图4所示:是小信号电阻和寄生在的栅极寄生电容表示小信号电阻和寄生在MPASS门口的电容。小信号分析产生直流增益的表情和的位置极点和零点,具体如下:

(10)

其中,

(11)

(12)

(13)

图3.所提出的LDO示意图

电流反射镜M3-M4引入了一个高频率,这可表示为:

(14)

等式(10)表明,通过利用交叉耦合的输入级与当前循环技术可以得到与[3]中所提出的LDO的.The增益LDO的增益相比更高的环路增益沿增加一个因子K

(15)

如果单位增益频率和相位裕度,调节器可写为:

(16) (17)

图4:所提出的LDO的小信号模型,如图3所示

- 仿真结果

允许与[3]中所提出的LDO,上述单位增益配置进行了测试,以1V的基准电压中所述的LDO公平的比较。图5示出它的环路增益的频率特性:注意,低频增益大于60dB过负荷电流的整个范围。图6示出LDO的相位裕量有与负载电流,两个负载电容器。,这是一个LDO可接受在轻负载:在PM值达到其最小值在高负载电容(100pF)和最小负载电流(1uA)。

图7描绘在LDO两个电容器值的负载瞬态响应;负载电流从为10uA脉冲至100mA的上升时间和下降1us。这个试验表明,在LDO是稳定的,即使在小负载和该输出冲保持在一个可接受的值,274mV。

图8提出了到线路瞬态响应;线路电压从1.4V脉冲至1.8V与上升和下降的为1us。最大输出的变化仅仅是267mV。

图5:开环交流响应

图6:不同负载电流和输出电容器拟议LDO的相位裕量

表II提供建议的LDO和几个类似的作品之间的性能比较。品质因数,,在使用[3]有用于:低的FOM值,在第二部分中描述的较好的瞬态性能.The EA,以高转换率和低静态目前,有助于使提出的LDO三个FOM比它的同行更好的三千次。

图7:LDO的瞬态负载(a)COUT =100pF,(B)COUT =10 pF

图8:两个负载电容建议为LDOIload=10uA的瞬态线:(a)COUT =100pF,(b)COUT =10 pF

表II。几种LDO的性能比较

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[497866],资料为PDF文档或Word文档,PDF文档可免费转换为Word

|

参数 |

【1】 |

【3】 |

【7】 |

这种材料 |

|

年 |

2010 |

2013 |

2012 |

2015 |

|

CMOS(微米) |

0.35 |

0.18 |

0.35 |

0.18 |

|

电源电压(V) |

4-6 |

1.2 |

2.5-4 |

1.8 |

|

输出电压(V) |

2.5 |

1 |

2.35 |

1 |

|

漏失电压(MV) |

200 |

200 |

150 |

90 |

|

Iout (mA) |

250 |

100 |

100 |

100 |

|

Iq (micro;A) |

20 |