英语原文共 10 页,剩余内容已隐藏,支付完成后下载完整资料

8T SRAM单元作为超越von-Neumann计算的多位点产品引擎

摘要:

大规模数字计算几乎完全依赖于von-Neumann架构,该架构由用于存储和计算的独立单元组成。从存储器单元到计算核心的能量昂贵的数据传输导致众所周知的von-Neumann瓶颈。旨在绕过von-Neumann瓶颈的各种方法正在文献中进行广泛研究。这些包括基于CMOS和超越CMOS技术的内存计算,其中通过对存储器阵列进行修改,可以尽可能靠近存储器单元执行矢量计算。有趣的是,基于CMOS技术的存储器内技术由于无处不在的场效应晶体管的存在以及由此产生的大规模制造和商业化的容易性而具有特别重要的意义。另一方面,也许机器学习等应用所需的最重要的计算包括点积运算。已经证明,新兴的非易失性忆阻技术在以原位方式计算模拟点产品方面非常有效。与数字矢量存储器内逐位布尔计算相比,点积的忆阻模拟计算导致更快的操作。然而,大规模制造方面的挑战加上忆阻器的有限耐久性阻碍了基于忆阻的计算解决方案的快速商业化。在这项工作中,我们表明标准8晶体管(8T)数字SRAM阵列可以配置为类似模拟的内存多位点产品引擎。通过将适当的模拟电压施加到8T SRAM阵列的读取端口并感测输出电流,可以实现近似的模拟 - 数字点积引擎。我们提出了两种不同的配置,用于在8T SRAM单元阵列中实现多位点积计算,而无需修改标准位单元结构。我们还证明了本方案在存在非理想性(如线路电阻和晶体管阈值电压变化的影响)时的鲁棒性。由于我们的提议保留了标准的8T-SRAM阵列结构,因此它可以用作具有标准读写指令的存储元件,也可以用作按需模拟类点产品加速器。

索引术语 - 内存计算,SRAM,冯诺依曼瓶颈,卷积,点积。

1.1介绍

最先进的计算平台广泛基于von-Neumann架构[1]. von-Nuemann架构的特点是用于计算和存储的不同空间单元。由于两个实体之间的频繁数据传输,这种物理上分离的存储器和计算单元导致巨大的能量消耗。此外,通过专用的有限带宽总线传输数据限制了整体计算吞吐量。由此产生的内存瓶颈是数据密集型应用程序(如机器)的硬件实现的主要吞吐量问题学习,人工智能等。

面向von-Neumann机器之外的高吞吐量的可能方法是实现以紧密交织的存储和计算能力为特征的分布式计算。如果计算可以在存储器阵列内部执行,而不是在空间上分离的计算核心中执行,则计算吞吐量可以显着增加。因此,人们可以想到在硅芯片上普遍存在的计算,其中逻辑核和存储器单元都参与计算操作。针对点产品计算已经提出了关于新兴非易失性技术的“内存中”计算的各种提议[2],[3]以及向量布尔运算[4]. 基于新兴技术的原型可以在中找到[3], [5] .

关于CMOS技术,已经提出了布尔内存操作[6] 和[7]. 在[6] 作者使用6T SRAM单元呈现了矢量布尔运算。另外,作者在[7] 已经证明8个晶体管(8T)SRAM单元由于它们的读取和写入端口分离而容易作为矢量计算原语。两件作品[6] 和[7] 基于向量布尔运算。然而,可能是机器学习等众多应用所需的最频繁和计算密集型功能是点积运算。基于电阻RAM(Re-RAM)的忆阻器在许多工作中已被报道为模拟点积计算引擎[4], [8]. 很少有基于SRAM单元中的模拟计算的工作可以找到[9], [10]. 这两种工作都使用6T SRAM单元并依赖于位线(BL)上的合成累积电压。不仅6T SRAM容易发生读干扰故障,故障也是BL上电压的函数。这导致了针对所提出的基于6T SRAM的模拟计算的严格约束的设计空间。在本文中,由于隔离的读取端口,我们使用的8T单元与6T单元相比更加稳健。我们表明,如果不修改8T SRAM单元的基本位单元,就可以将8T单元配置为内存中的点积计算。请注意,与之前使用CMOS技术进行内存计算的工作形成鲜明对比的是,我们使用强大的数字8T位单元实现基于电流的模拟点积计算。

本工作的主要亮点如下:

1)我们表明,传统的8T SRAM单元可以用作模拟类点积计算的基元,而无需修改位单元电路。此外,我们提出了两种不同的配置,用于使用8T单元进行点积计算。

2)除了包括8T单元的读端口的各个晶体管的尺寸外,还有基本的位单元结构保持不变。因此,8T SRAM阵列也可用于通常的数字存储器读写操作。因此,所呈现的8T单元阵列可以充当专用点产品引擎或作为按需点积产品加速器。

3)已经报道了使用45nm预测技术模型的详细模拟分析,包括布局分析和非理想性的影响,例如线电阻的存在和晶体管阈值电压的变化,突出了两种提出的配置中的每一种所呈现的各种权衡。

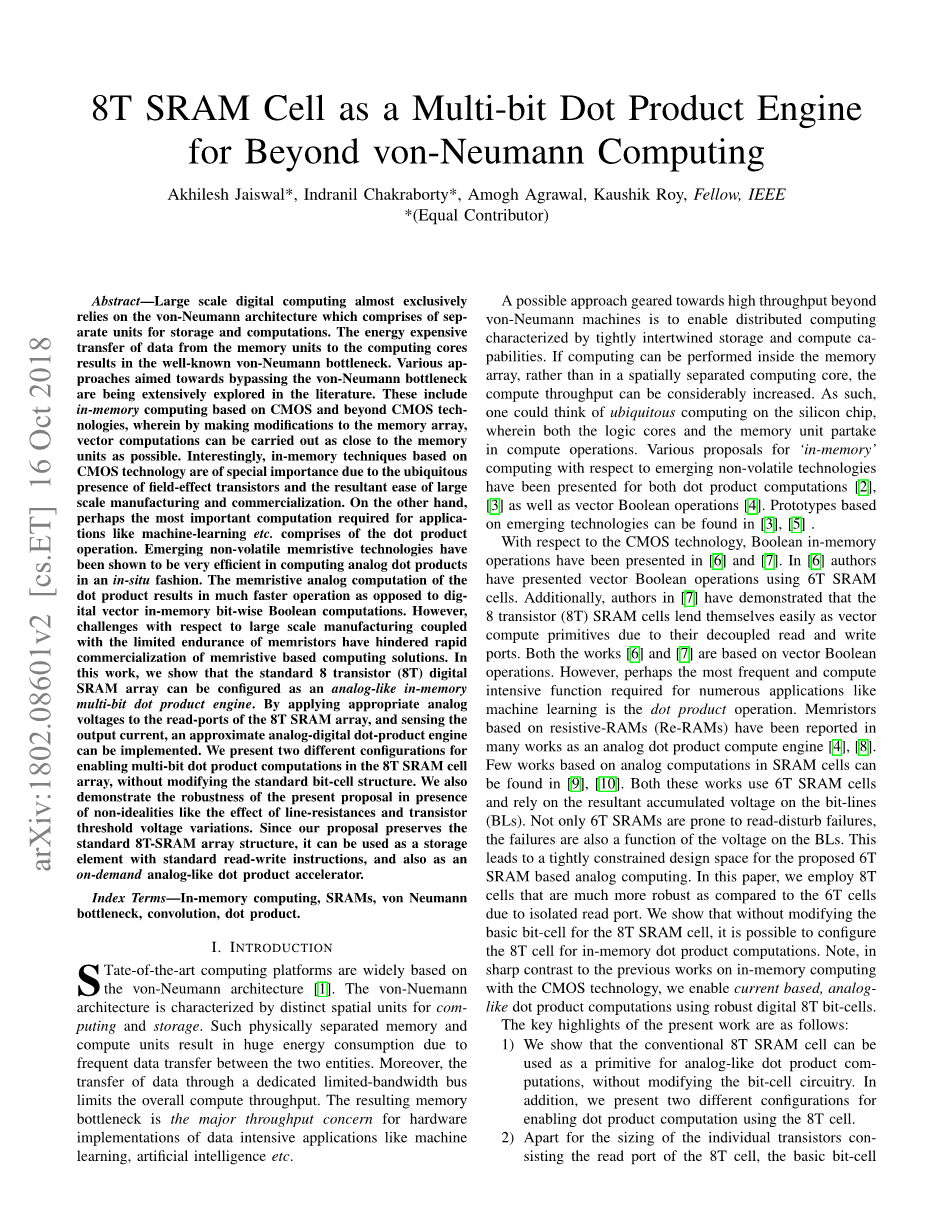

图1:(a)标准8T-SRAM位单元的示意图。它由两个分离的端口组成,分别用于读写。(b)首先提出的配置(Config-A),用于使用8T-SRAM位单元实现点积引擎。SL连接到输入模拟电压vi,RWL接通。检测到通过RBL的电流Irbl 并且与点积vi gi成比例,其中gi 是晶体管M 1和M 2的ON / OFF电导。(c)第二个提议的配置(Config-B)。输入模拟电压施加到RWL,而SL则提供恒定电压V偏压。通过RBL的电流以与Config-A中相同的方式被感测。

·

1.2 8t-sram作为点积引擎

传统的8T位单元示意性地示于图1中。1(a). 它由众所周知的6T-SRAM位单元和两个额外的晶体管组成,这些晶体管构成一个去耦读端口。为了写入单元,写入字线(WWL)被使能,并且写入位线(WBL / WBLB)被驱动到Vdd 或接地,这取决于要存储的位。为了从单元读取值,读取位线(RBL)被预充电到Vdd 并且读取字线(RWL)被使能。注意,源线(SL)连接到地面。根据位单元是否存储逻辑“1”或“0”,RBL分别放电至0V或保持在Vdd。RBL的最终电压由读出放大器读出。虽然8T细胞会发生

与6T设计相比,位单元面积增加约30%,由于单独读取,它们具有无干扰读取和更强大的功能并编写路径优化[11].

我们现在展示这样的8T-SRAM如何在不影响存储在SRAM单元中的位的稳定性的情况下,对基本位单元电路没有修改(除了读取晶体管的大小)之外,可以表现为点积引擎。我们提出了两种配置 - Config-A和Config-B在8T-SRAM中实现点积运算。Config-A如图1所示。1(b). 输入vi (编码为模拟电压)被施加到SRAM阵列的SL,并且RWL也被使能。RBL连接到感应电路,我们将在后面描述。因此,存在从SL到RBL的静态电流,其与输入vi 和两个晶体管M 1和M 2的电导成比例。为简单起见,假设权重(存储在SRAM中) )具有单位精度。如果位单元存储#39;0#39;,则晶体管M 1截止,并且通过RBL的输出电流接近0.然而,如果位单元存储#39;1#39;,则电流与v成比例i g上 ,其中g上 是晶体管的串联“导通”电导。假设对于存储器阵列的每一行,在SL上应用类似的输入vi 。由于RBL在整个列中是通用的,因此来自所有输入vi 的电流被加总到RBL中。此外,由于SL在每行中是公共的,因此相同的输入vi 被提供给多列。因此,通过每列的RBL的最终输出电流与Ij =Sigma;(vi gj)成比例,其中gj 是晶体管的“ON”或“OFF”电导,取决于第i行和第j列中的位单元是否分别存储#39;1#39;或#39;0#39;。因此,输出电流矢量类似于矢量矩阵点积,其中矢量是输入模拟电压形式的vi ,矩阵是gj ,作为数字数据存储在SRAM中。现在让我们考虑权重的4位精度。如果权重W j = wwww,其中w是比特对应于4位权重,向量矩阵点产品变成:

Sigma;(vi · Wi ) = Sigma;[vi · (23w3 22w2 21w1 w0)]

j

= Sigma;(vi · 23w3) Sigma;(vi · 22w2) Sigma;(vi · 21w1) Sigma;(vi · w0)

现在,如果我们调整读取晶体管M1和M2的大小

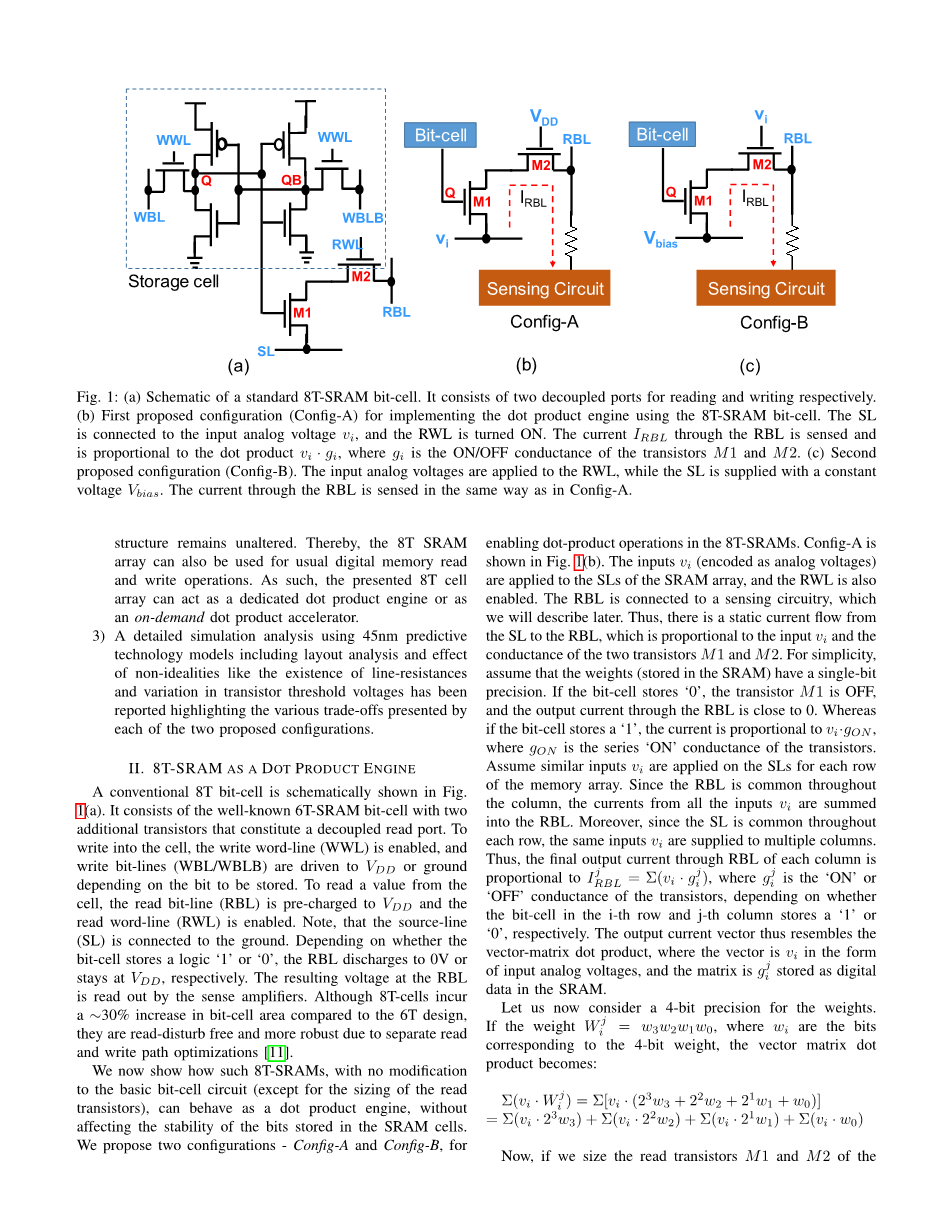

图2:用于计算点积的8T-SRAM存储器阵列

具有4位重量精度。仅显示读取端口,未显示6T存储单元和写入端口。阵列列分为四列,晶体管M 1和M 2的四个列的比例为8:4:2:1。输出电流Ij 表示四列的Irbl的加权和,其近似等于期望的点积。

乌特

第1列到第4列中的SRAM位单元,比率为23 :22 :21:1,如图2所示。

2.晶体管电导

#39;ON#39;状态也将是比率23 :22 :21 :1。

因此,通过四列的RBL对电流求和,根据上面所示的等式产生所需的点积。可以在整个阵列中重复该尺寸调整图案。此外,还可以使用具有不同阈值电压的晶体管来模拟所需的电导率,如23 :22 :21 :1。注意,电流

通过四个连续列的RBL求和

因此,我们为每组四列获得一个模拟输出电流值。换句话说,存储在SRAM阵列中的数字4位字乘以输入电压vi ,并通过RBL上的电流的模拟相加来求和。这种在数字存储器阵列中的向量乘法和求和的一次性计算将导致点积的高吞吐量计算。

值得一提的是,输入vi 乘以存储的权重并总结的方式让人联想到忆阻点积计算[8]. 然而,所提出的基于SRAM的计算的一个问题是,与典型的忆阻器导通电阻(几十千欧姆的范围)相比,晶体管的导通电阻(几千欧姆)要低得多。[12]. 因此,在所提出的提议中,流过ON晶体管M 1和M 2的静态电流通常会高得多。为了减少静态电流,我们建议缩小SRAM单元的电源电压。值得注意的是,已知8T电池即使在高度缩放的电源电压下也能保持稳健的工作[13]. 在下一节中,我们使用的Vdd 低于1V的标称Vdd 。我们现在将描述另一种减少电流的方法,尽管需要权衡,如下所述。

Config-B如图1所示。1(c). 这里,SL是连接的到恒定电压V偏压。输入向量vi 连接到RWL,即M 2的门。类似于Config-A,输出电流Irbl 与vi成比例。我们稍后将从模拟中显示,对于一定范围的输入电压值,我们得到Irbl 和vi之间的线性关系,可以被利用来计算近似点积。为了实现多位精度,晶体管尺寸调整以与Config-A相同的方式完成,如图2所示。2, 所以这样Irbl 与晶体管电导成正比。所提出的Config-B的主要特征如下。输入电压vi 具有容性负载,与a相反Config-A中的电阻负载。这放宽了对输入电压发生器电路的限制,并且在级联点产品引擎的两个或更多个级时是有用的。但是,作为在下一节中,Config-B具有与零输入相对应的小的非零电流,而不是Config。零输入零电流。

为了检测RBL的输出电流,我们使用电流到电压转换器。这可以最简单地是一个电阻器,如图1所示。1. 但是,有一些限制。随着输出电流的增加,输出电阻两端的压降也会增加,从而改变所需的电流输出。RBL上的电压的变化也将改变晶体管M1和M2两端的电压,从而使它们的电导成为RBL上的电压的函数。因此,在对应于多个的较高电流下 储存器阵列的行不接近矢量矩阵点积,但偏离理想输出。RBL电压对电流Ir

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[439607],资料为PDF文档或Word文档,PDF文档可免费转换为Word