英语原文共 6 页,剩余内容已隐藏,支付完成后下载完整资料

TIME:基于忆阻器的深度神经网络的内存训练架构

摘要

神经网络(NN)的训练通常是耗时且资源密集的。忆阻器已经显示出其在计算NN方面的潜力。特别是对于金属氧化物电阻随机存取存储器(RRAM),其横杆结构和多位特性可以高精度地执行矩阵矢量积是NN最常见的操作。但是,实现NN的培训存在两个问题。首先,当前的体系结构只能支持相应的训练,并且不能执行反向传播(BP),即NN的权重更新。其次,NN的训练需要大量迭代并不断更新权重以达到收敛,由于大量的写入和读取操作,导致了大量的能量消耗。在这项工作中,我们提出了一种新颖的架构,TIME和外围电路设计,以便在RRAM中训练NN。 TIME支持BP和权重更新,同时最大化外围电路的重复利用,以便在RRAM上进行推理操作。同时,设计了无变化调谐方案和逐步写入电路,以降低调谐RRAM的成本。我们在TIME中开发了SL(监督学习)和DRL(深度强化学习)的表现,并 且引入了特定的DRL映射方法,进一步提高了能源利用率。实验结果表明,在SL中,与大多数功率应用特定电路(ASIC)的测量相比,TIME平均可以实现5.3倍的高能效。 在DRL中,TIME在能源利用率方面平均比GPU高出126倍。如果调整RRAM的成本可以进一步降低,那么与ASIC相比,TIME有可能将能源效率提高2个数量级。

- 引言

最近,神经网络(NN)和深度学习在许多领域不断取得突破[1]。基于NN的监督学习(SL)和深度强化学习(DRL)已被证明是分类和学习政策的有力工具。他们甚至在某些领域中表现优于人类专家,例如ImageNet [2]中的物体分类和玩Atari游戏[1]。

处理单元(PU)和存储器之间的数据移动一直是各种计算系统中最关键的性能瓶颈。

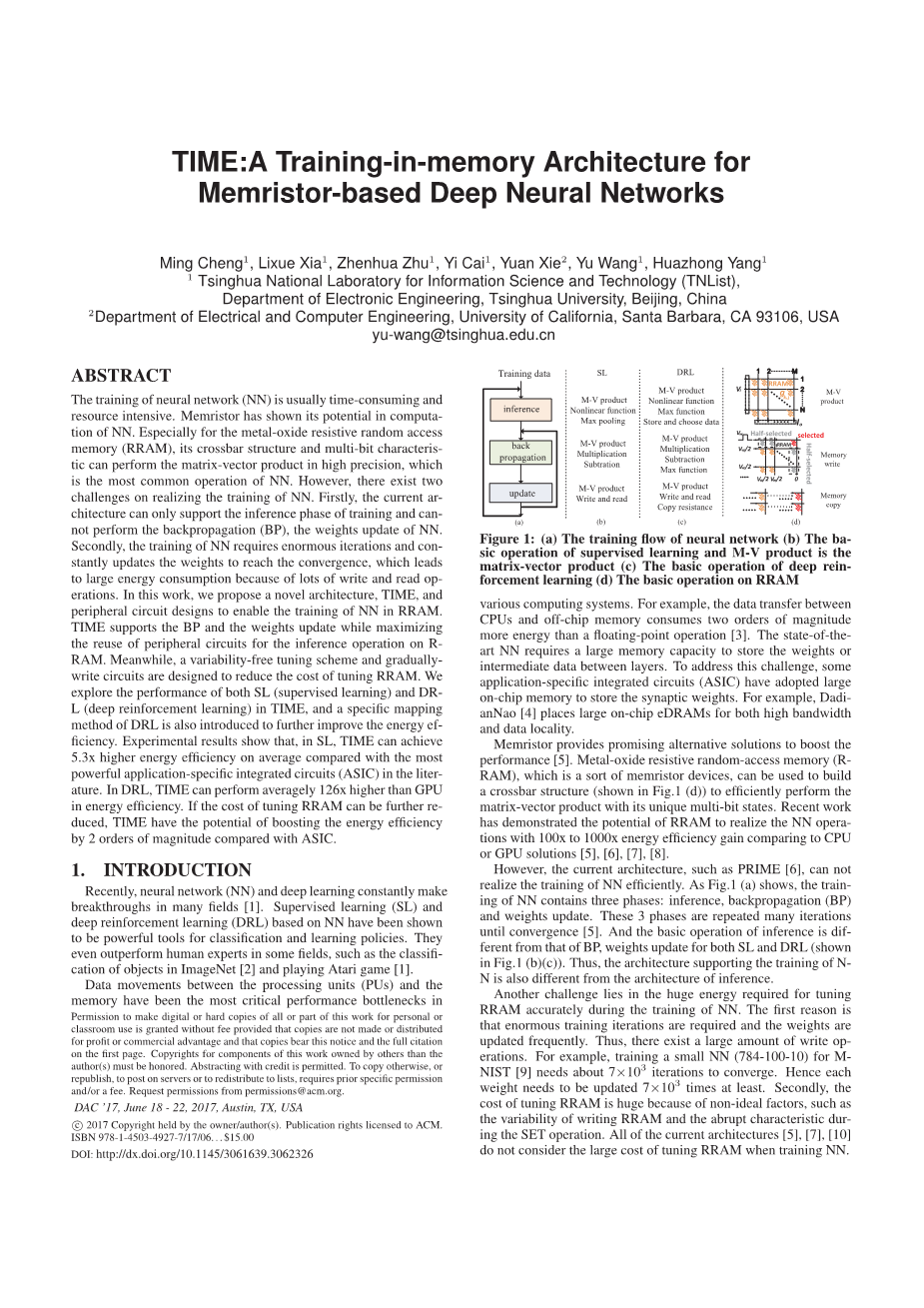

图一:(a)神经网络的训练流程(b)监督学习的基本操作流程和M-V乘积是矩阵向量积(c)深度加强学习的基本操作(d)RRAM的基本操作

例如,CPU和片外存储器之间的数据传输比浮点运算消耗了两个数量级的能量[3]。最新状态NN需要较大的存储容量来存储层之间的权重或中间数据。为了应对这一问题,一些应用特定的集成电路(ASIC)采用了大型片上存储器来存储突触权重。例如,DadianNao [4]为高带宽和数据局部放置了大型片上eDRAM。

忆阻器有望提供提升性能[5]的替代解决方案。金属氧化物电阻随机存取存储器(RRAM)是一种忆阻器器件,可用于构建交叉杆结构(如图1(d)所示),以便有效地执行具有多比特状态的矩阵向量积。最近的工作已经证明了与CPU或GPU解决方案相比, RRAM实现NN操作的潜力,其能量效率提高了100倍至1000倍[5],[6],[7],[8]。

以目前的架构,如PRIME [6],仍然无法有效地实现NN的训练。如图1(a)所示,NN的训练包含三个阶段:推理,反向传播(BP)和权重更新。这三个阶段重复多次迭代直到收敛[5]。并且推理的基本操作不同于BP,SL和DRL的权重更新(如图1(b)(c)所示)。因此,支持NN训练的架构也与推理架构不同。

另一个问题在于在NN训练期间准确调整RRAM需要的巨大能量。一个原因是需要进行大量的训练迭代并且经常更新权重。因此,存在大量写入操作。例如,为MNIST [9]训练一个小的NN(784-100-10)需要大约7times;103次迭代才能收敛。因此,每个重量至少需要更新7times;103次。其次,由于非理想因素,例如写入RRAM的可变性和SET操作期间的突然特性,调整RRAM的成本是巨大的。所有当前的架构[5],[7],[10]都没有考虑在训练NN时调整RRAM所带来的巨大成本。

在本文中,我们提出了一种新的体系结构,称为TIME,用于在RRAM存储器中实现NN的训练。此外,设计了无变化调谐方案和逐步写入电路,以降低调整RRAM的成本。本文的主要贡献如下:

1.我们建议使用PRIME中的TIME(Training-In-Memory)和外围电路的修改来进一步支持反向传播和权重更新操作。实验结果表明,与最近的ASIC解决方案相比,TIME可以将SL的平均能量效率提高5.3倍[4]。提出了一种特定的映射方法来支持DRL的训练。与GPU相比,TIME将能量效率提高了126倍,与直接映射方法相比,特定的映射方法提高了1.2倍的能源利用率。

2.我们提出了一种无变化调整方案,以降低写入和读取RRAM的频率,以及逐步写入电路,旨在克服写入RRAM的不对称性。结果显示可变性自由调整方案和逐步写入与[11]相比,电路可以将能量效率提高2.7倍。如果能够降低写入RRAM的能量,则与ASIC解决方案相比,能量利用率可以提高到2个数量级[4]。

2.准备工作

2.1 RRAM设备基础

调整RRAM包括两种方式:SET和RESET。 SET操作将RRAM的电阻从高电阻状态(HRS)调谐到低电阻状态(LRS).RESET操作是反向操作。 根据[12],SET操作导致RRAM的电阻突然改变,而RESET操作可以逐渐调整。 此外,SET操作和RESET操作都存在可变性[12]。 因此,将RRAM调整为目标电阻值取决于迭代RESET操作和SET操作[11],但这种方法显然增加了调整RRAM的成本。

2.2监督学习

SL的训练如图1(a)所示,它包含3个阶段:推理,BP和更新[7]。

SL的推断图1(b)表明推理[13]包括3个运算:矩阵向量乘积,非线性函数,表示为公式(1)和最大池化,用公式2表示。

(1)

其中x和y分别是NN的输入和输出。 W是NN的权重,b是偏差矢量[11]。

(2)

其中x1,x2,...,xn是最大池化函数的输入,x是最大池化函数的输出。SL的反向传播图1(b)显示BP包括3种基本操作:矩阵矢量积,乘法,减法[13]。BP过程按顺序表示为公式(3),(4),(5),

(3)

(4)

(5)

其中,,分别表示空间输出,目标输出,第l层的权重。 是第l层中的目标输出和输出之间的第l个差异。是BP的误差式。(3)在最终层进行。 然后,公式(4)和公式(5)迭代地按顺序实现。

SL的更新 该更新包括3个操作[13]:写入,读取,矩阵向量乘积,表示为公式(6),

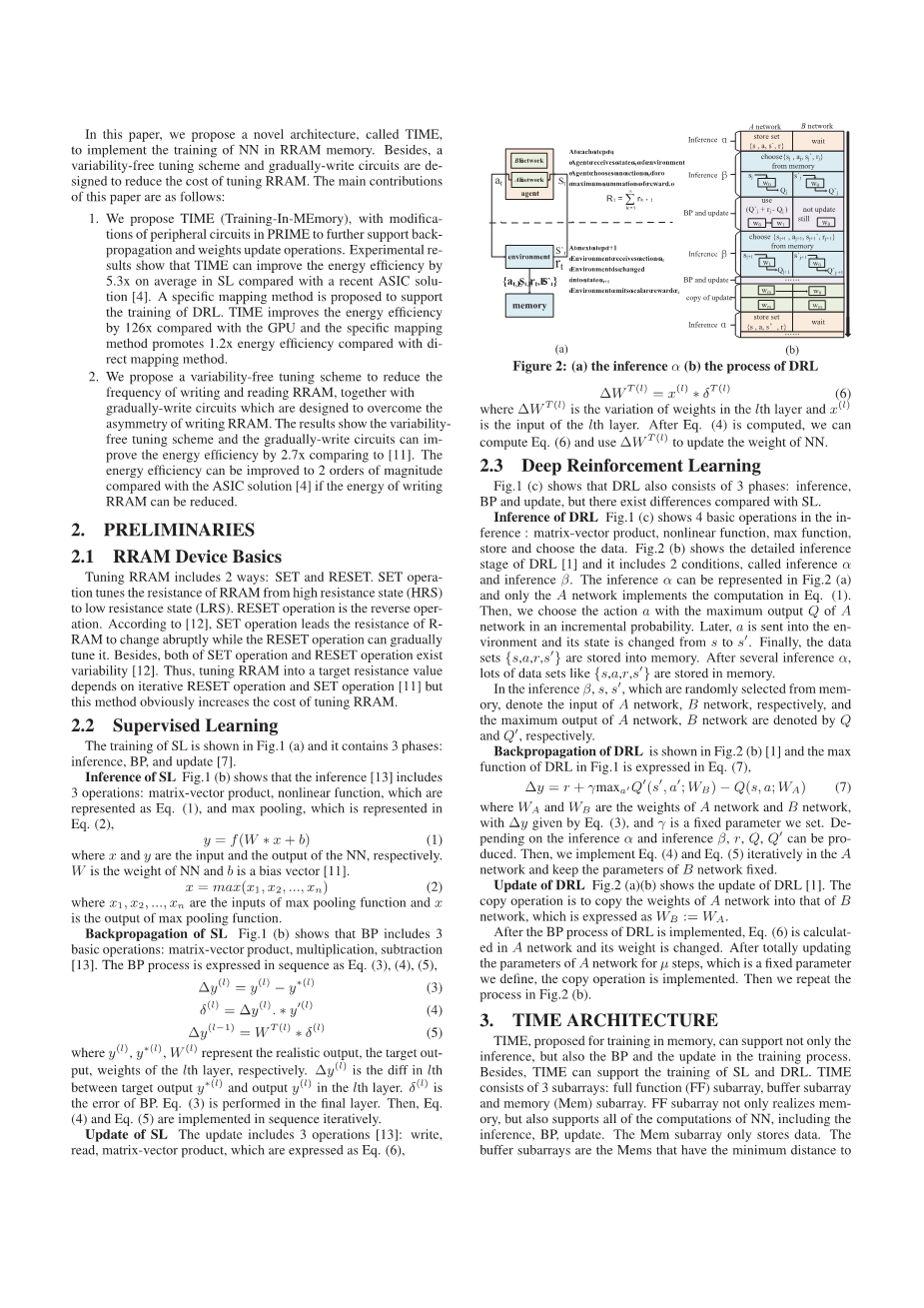

图二 (a)推理alpha;(b)DRL的处理

(6)

其中是第l层中权重的变化,是第l层的输入。 在公式(4)计算,我们可以计算公式(6)并使用来更新NN的权重。

2.3深度强化学习

图1(c)显示DRL也包括3个阶段:推理,BP和更新,但与SL相比存在差异。

DRL的推断图1(c)显示了推理中的4个基本操作:矩阵向量积,非线性函数,最大函数,存储和选择数据。图2(b)显示了DRL [1]的详细推理阶段,它包括2个条件,称为推理alpha;和推理beta;。推理alpha;可以在图2(a)中表示,并且只有A网络在公式1中实现计算。然后,我们以增量概率选择具有A网络最大输出Q的动作a。之后,a被发送到环境中,其状态从s变为srsquo;。最后,数据集{s,a,r,srsquo;}存储在存储器中。经过几次推理后,许多数据集如{s,a,r,srsquo;}都存储在内存中。

从记忆中随机选择的因子beta;,s,s分别表示A网络,B网络的输入,A网络的最大输出,B网络分别用Q和Q表示。

DRL的反向传播 如图2(b)[1]所示,图1中DRL的最大函数用公式(7)表示。

其中和是A网络和B网络的权重,其中由公式(3)给出,gamma;是我们设定的固定参数。根据推断alpha;和推论beta;,可以产生r,Q,Qrsquo;。 然后,我们执行公式(4)和公式(5)在A网络中迭代并保持B网络的参数固定。

DRL的更新 图2(a)(b)显示了DRL [1]的更新。 复制操作是将A网络的权重复制到B网络的权重,表示为:= 。

在实施DRL的BP流程之后,公式(6)在A网络中计算并且其权重被改变。 在完成mu;步骤的A网络参数更新后,这是我们定义的固定参数,实现了复制操作。 然后我们重复图2(b)中的过程。

3.TIME 结构

建议用于记忆训练的TIME不仅可以支持推理,还可以支持BP和训练过程中的更新。此外,TIME可以支持SL和DRL的培训。 TIME由3个子阵列组成:全功能(FF)子阵列,缓冲子阵列和存储器(Mem)子阵列。 FF子阵列不仅实现了内存,还支持NN的所有计算,包括推理,BP,更新。 Mem子阵列仅存储数据。缓冲区子阵列是与FF子阵列具有最小距离的Mems,其可以利用高带宽来存储中间数据。

图(3):TIME体系结构。 左:内存库结构。 右:TIME的功能块改造/添加。(a)带有多级电压源的字线驱动器; (b)具有模拟减法和S形电路的列多路复用器; (c)实施激活衍生物的预处理; (d)用于计算最终层中差异的最终输出差异; (e)FF与缓冲区子阵列之间的连接; (f)TIME控制器; (g)具有多级输出计数器的可重新配置的SA,并增加了修正线性单元,最大功能和更新权重

3.1 外围电路设计

为了在FF子阵列中实现NN的训练,如图3所示,我们将预处理和最终输出差异添加到FF子阵列中,我们修改字线解码器和驱动器(WDD),列多路复用器(Col MUX),感测放大器(SA)和控制器。

WDD图3(a)显示WDD用于准备NN的输入数据并提供写入和读取RRAM的电压。 WDD必须支持来自RRAM交叉开关的字线(WL)或来自RRAM交叉开关的位线(BL)的数据,以便在推理和BP中重用它。因此,为了隔离BP和推理,两个传输门(TG)分别与字线和位线连接。通过这种低成本设计,推理和BP重复利用相同的WDD。 WDD的其他部分与PRIME相同。多电平电压源用于产生多电平电压,而开关电路(SW)用于确保所有输入数据可以同时馈入RRAM交叉开关的WL。此外,放大器用于驱动WL,写入驱动器(WD)用于修改RRAM器件的电阻值。

ColMUX如图3(b)所示。与WDD类似,为了重用Col MUX,将两个传输门添加到Col MUX的输入以隔离NN的推断和BP。其他部分与PRIME相同。Sigmoid用于实现NN的S形函数,2个交叉柱之间的减法用于计算矩阵向量积。用MUX,我们可以选择sigmoid,减法和RRAM交叉开关之间的输出,它输出RRAM的电阻值。

SA缺少读出放大器,实现模数转换,精密控制,ReLU功能,最大功能和更新选择,如图3(g)所示。两个公式(7)DRL和公式(2)SL都可以实现最大功能。池是用公式(2)计算的。在PRIME中通常会找到4个值的最大值,但DRL通常会在4个以上的值中找到它,例如[1]中的18个值。因此,我们添加了更多的寄存器和相应的MUX来切换池和DRL中的最大功能。此更改仅出现在一个SA中,因为DRL的最大功能仅在NN的最终层中计算。更新的权重用于根据权重变化Delta;W的符号选择需要更新哪个交叉开关。详细介绍了这个问题。用于实现模数转换和精确控制的这些电路用于克服精度的困难。这两部分与PRIME [6]相同。

最终输出微分 图3(d)显示了最终输出微分的设计,它用于计算公式(3)级公式(7)的减法。因此,减法器用于最终差异计算。此外,DRL还有一个加法器来计算Qrsquo;的加法和公式(7)中的r,用于产生DRL的目标输出。我们应该注意的是,最终的输出差异只存在一次,因此它会导致非常低的能量和面积成本。与PRIME相比,最终的输出差异是一个新的电路。

预处理 如图3(c)所示,预处理用于计算公式(4)中的导数。根据公式(4)和公式(6),Delta;W需要delta;,这是yrsquo; 和Delta;y之间相乘的结果。为了得到sigmoid和ReLU中的yrsquo;,设计了预处理。根据[13],比较器(Comp)可以计算ReLU函数的导数。对于sigmoid函数[13],减法器和乘法器可以计算sigmoid函数的导数。此外,我们重用图3(c)中的乘数来实现delta;y和y?的乘法。与PRIME相比,预处理是一种新的电路。

控制器 如图3(f)所示。它主要用于提供FF子阵列中的控制信号。控制器的关键功能是在不同模式之间配置FF子阵列。与存储和推理两种模式的PRIME相比,TIME中的控制器增加了三种模式:BP,更新,DRL。

连接 如图3(e)所示,根据FF子阵列和缓冲子阵列之间的专用连接,FF子阵列产生的中间数据可以存储在具有高带宽和低成本数据移动的缓冲子阵列中。

3.2 SL的培训实施

推论 图4(a)显示了第一层NN。首先,蓝线和箭头表示样本(x *,y *)被送入TIME的Mem子阵列。然后,将(x *,y *)从Mem子阵列发送到缓冲子阵列。接下来,通过缓冲子阵列将第一层的输入x *传送到FF子阵列中。然后,将x *发送到交叉开关以实现公式(1)中的矩阵向量乘积。同时,如粉红线所示,在执行公式(6)中的操作之前,将x *写入另一个交叉开关。其他层的状况相似。输入被发送到两个交叉开关以实现NN的推断,并且它同时存储到另一个FF子阵列中。这两个并行操作可以加速培训。

如图4(a)的棕色线所示,数据在公式(1)之后被分成2部分。一部分被发送到下一层NN的交叉开关

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[442990],资料为PDF文档或Word文档,PDF文档可免费转换为Word