英语原文共 5 页,剩余内容已隐藏,支付完成后下载完整资料

基于65nm低功耗CMOS技术的线性度增强型双吉尔伯特混频器

摘要 本文提出了一种利用创新型双吉尔伯特结构的下变频混频器。它是在65纳米低功率数字CMOS工艺中设计和制造的。混频器基于简单的吉尔伯特型结构混频器,并使用二阶混频器作为有源负载。第二混频器支路并联有开关能力的RC回路保证了高增益或高线性度的接入。在时钟频率为1.5GHz时测量得到一个值为11.1dBm的高三阶输入交调点。本文提出的结构实现了10.9dB的最大变频增益。在高增益设置下,该结构从幅值为1.2V的电源电压中消耗了仅6mW的功率。

关键词 下采样混频器、低功率、纳米CMOS技术、双吉尔伯特混频器

1 引言

现代移动设备的发展趋势主要是设备功能的数字化实现。市场需求需要设计者在一个移动设备上实现越来越多的功能。为了实现这个目标,不同模块的高密集封装是十分必要的。片上系统(SOC)方法的提出,使得电路的花费和寄生单元得以大大减少,满足了市场需求。在片上系统中,电路的模拟和数字部分都是由数字CMOS技术实现的。在电路的设计过程中,我们需要使用最新的低功耗CMOS技术来实现最大限度地提高数字部分的处理能力。在这种技术中,为了实现在数字电路中的低功耗,晶体管的参数需要不断优化,因此,晶体管的阈值电压达到很高。由于电路的模拟部分也要求在相同的技术下实现,所以,这一特性对于模拟电路设计者来说提出了一个极大的挑战。

为了实现与周围的世界通信,设备中的集成收发器是十分必要的。在通信过程中,如果需要涉及不同的通信标准,如:移动全球通信系统(GSM)、通用移动通信系统(UMTS)、全球定位系统(GPS/GALILEO)、无线局域网(WLAN)或其他标准,通常甚至会需要多个收发器。接收路径通常由一副天线,一个低噪声放大器(LNA)、一个下变频混频器、一个滤波器、一个模数转换器(ADC)和数字基带处理部分组成。在发送路径中,正好与接收路径过程相反,数据由数字信号处理产生,由数模转换器(DAC)转换为模拟信号,再经过滤波器和上变频混频器,将基频频率转换为射频频率,最后由功率放大器(PA)将信号传送给天线并定向发射出去。图1展示了两种路径的各模块组成。

图1 软件定义无线电的发射和接收路径

在接收路径中最关键的一个组件就是下采样混频器。由于它对整个接收电路链路的线性度的限制,因此,在接收器的前端,高线性度是十分重要的。方程式1显示了级联接收电路链路总的三阶交调点(IIP3),它被每一级的增益和三阶交调点(IIP3)影响着。

在这篇文章中,我们想要提出一种能用于1.5GHz应用的下变频混频器,例如:GPS/GALILEO。在下一节中,我们将要提出一种先进的混频器电路结构,通过对该结构的分析,我们在论文的最后,会给出具体的仿真结果和实物测量结果,同时利用表格总结各性能参数,并对本文所参考的文献所提出的的结构的各性能参数作出比较。

2 电路描述

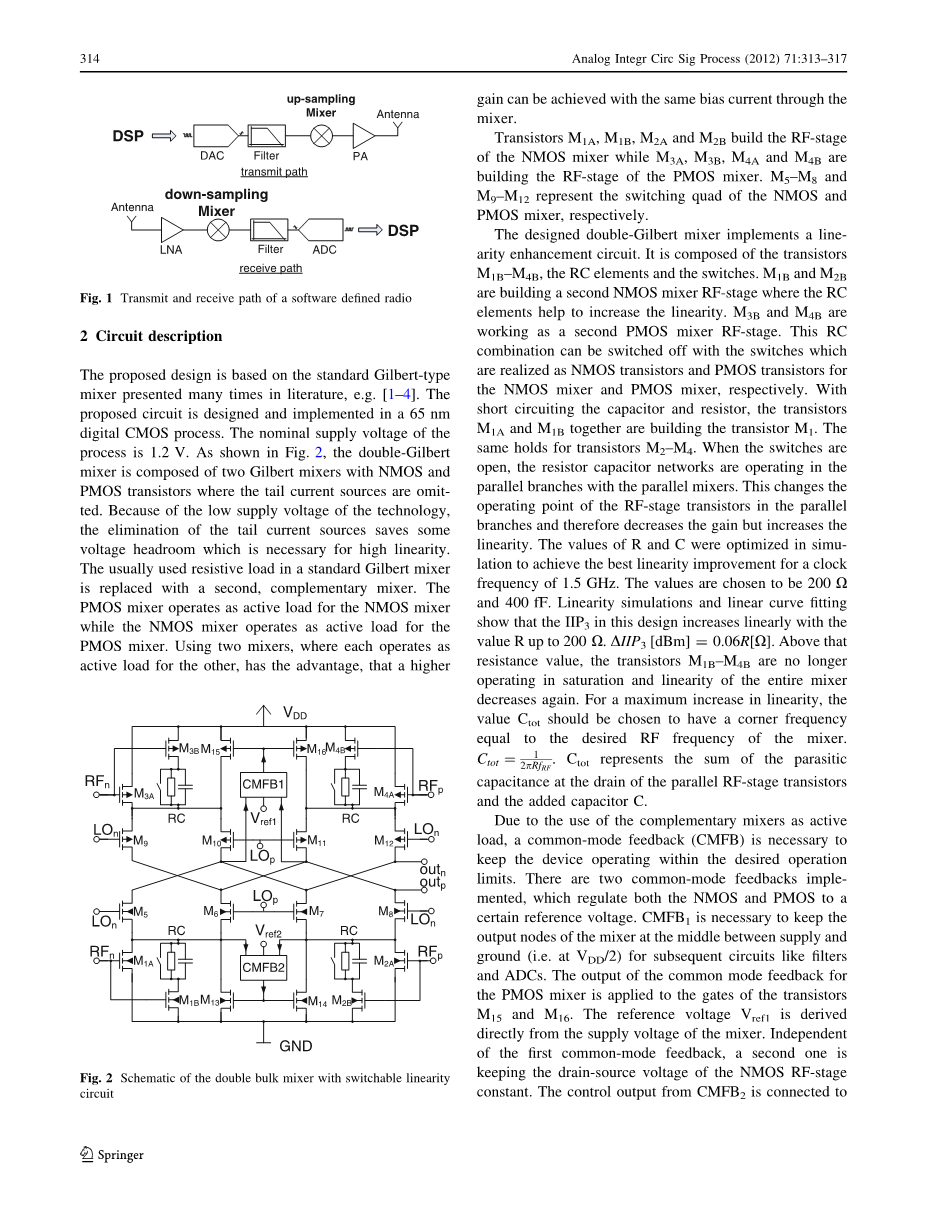

本文提出的设计是基于标准的吉尔伯特结构混频器结构,该结构在文献[1-4]中多次提出。本文所提出的电路是基于65nm的数字CMOS工艺中设计和实现的。该工艺所需要的标称电源电压为1.2 V。如图2所示,双吉尔伯特结构混频器由具有NMOS和PMOS晶体管的两个吉尔伯特混频器组成,该结构使得尾电流源得以消除。由于该技术工作在低电源电压条件下,尾电流源的消除节省了高线性度所必需的电压余量。标准吉尔伯特混频器中常用的电阻性负载由二阶互补的混频器替代。PMOS混频器用作NMOS混频器的有源负载,同时,NMOS混频器也作为PMOS混频器的有源负载。两个混频器的使用,且其中一个混频器作为另外一个的有源负载,使得该结构具有在混频器相同偏置电流下得到更高增益的优点。

晶体管M1A,M1B,M2A和M2B构成了NMOS混频器的射频端,而PMOS混频器的射频端晶体管M3A,M3B,M4A,M4B构成。晶体管M5-M8和M9-M12分别构成了NMOS和PMOS混频器的四路开关。该开关的作用是作为作为LO信号的选通,当LO为高电平信号时,NMOS管M5、M7和PMOS管M10、M12导通,当LO为低电平信号时,NMOS管M6、M8和PMOS管M11、M13导通。由于开关对的半周期导通性,输出的差分信号得到的增强,获得了较高的增益,同时也使得噪声系数得到减小,达到较好的性能。

本文所设计的双吉尔伯特混频器实现了一个线性度增强的电路结构。该电路由晶体管M1B-M4B,RC回路和开关组成。晶体管M1B和M2B组成了二阶NMOS混频器的射频端,其RC回路有助于增加线性度。同时,晶体管M3B和M4B组成了二阶PMOS混频器的射频端。电路中的RC结构能够作为开关,分别为NMOS混频器和PMOS混频器选择NMOS晶体管和PMOS晶体管。在该结构中,当电容和电阻短路时,晶体管M1A和M1B共同构成了晶体管M1。该情况同样适用于晶体管M2-M4。当开关打开时,RC回路网络和并联的混频器工作在并联支路中,这种情况改变了在并联支路的射频端的晶体管的工作点,因此,电路结构的增益减少,而线性度增加。电阻R和电容C的值在仿真中被不断优化,以实现在时钟频率为1.5GHz时,电路的线性度得到最大化改善。最后的优化结果为电阻值为200Omega;,电容值为400fF。线性模拟和线性拟合曲线表明,在本次电路设计中,随着电阻值增加到200Omega;,三阶交调点增加了线性度。Delta;IIP3[dBm]=0.06R[Omega;]。超过上述电阻值,晶体管M1B-M4B无法工作在饱和条件下,而且整个混频器的线性度也大大下降。为了实现线性度的最大化增加,Ctot的值应适当选择使满足其角频率等于混频器所需的射频频率,Ctot=1/2pi*R*fRF。Ctot表示并联射频端晶体管漏极的寄生电容和附加电容C的总和。

由于本设计使用互补混频器作为有源负载,为了保证设备工作在期望的操作限制内,共模反馈(CMFB)回路的设计是十分必要的。结构中设计了两种共模反馈,它们分别用于调节NMOS和PMOS到一个特定的参考电压。共模反馈CMFB1用于保持混频器的输出节点的电压为电源对地电压的一半,即为VDD/2,该电压值为随后的电路如滤波器和模数转换器提供了有利的工作条件。PMOS混频器的共模反馈的输出端与晶体管M15、M16的栅极相连接。共模反馈回路的参考电压Vref1直接来源于混频器的电源电压。第一个共模反馈回路是独立的,而第二个共模反馈回路用于保持NMOS混频器的射频端的漏极电压稳定为一个常数。由共模反馈CMFB2的控制的输出与晶体管M13、M14的栅极相连接。两个共模反馈电路都用于实现单级运算跨导放大器(OTAs),该结构实现了控制点输出电压在内部的固定参考电压范围内。共模反馈CMFB1构成的放大器输入端接NMOS晶体管差分输入对,同时,共模反馈CMFB2构成的放大器输入端接PMOS晶体管差分输入对。单级运算跨导放大器的负载端接互易的镜像电流,这一负载在单端转换时表现出差分特性。

图2 具有可选择线性度的双混频器结构示意图

3 测试结果

本文所设计的双吉尔伯特混频器在65nm的数字低功耗CMOS技术中实现,我们分别规定N型晶体管和P型晶体管的阈值电压为VTHe=0.4V,VTHp=-0.5V。测量包括所有焊接点的总面积,最后芯片的总面积为785*485mu;m2,其中有效区域的面积仅为215*125mu;m2。芯片直接连接在印刷电路板(PCB)上。印刷电路板从SMA连接器到芯片的输入端设计有阻值为50Omega;的微带金属线。印刷电路板上进行工艺镀金,这对于芯片的连接是十分必要的。利用该工艺连接芯片能够有效地减小输入端的电感和电容。

图3 芯片实物图(上)和有效面积的版图(下)

连接在印刷电路板上的芯片示意图、混频器的有效区域的设计图及其尺寸如图3所示。我们在进行测试时,射频端输入和时钟信号输入都是差分信号。此时,从源端获取的有用的差分信号被外部的平衡转换器转换为单端信号。所有的测量都是用网络分析仪和频谱分析仪完成的,且所有的测量都在1.5GHz的时钟信号输入下进行。

不同的时钟信号功率使得本文所设计的混频器获得不同的增益。图4展示了在设置不同时钟信号功率时,所测量的双吉尔伯特结构混频器的增益VITout/VRFin随本地振荡功率变化的曲线示意图。从图上可以看出,当设置为较高时钟功率时,随着本地振荡器的时钟功率的增加,混频器的增益线性增加;当本地振荡器的时钟功率增大到0dBm时,超过该功率后的增益表现了一定的压缩性。经过不断测试,在本地振荡器的时钟功率为7dBm时,混频器的增益达到最大值。

在确定了混频器的最大增益后,我们使用网络分析仪测试该结构的1dB压缩点,该测试在网络分析仪的频分偏置模式下进行。图5展示了利用单音测试方式得出的在高频和低频两种设置条件下的混频器的1dB压缩点。该测试输入功率为7dBm,中心频率为1.5GHz的本地振荡信号。在射频输入端,我们输入功率能够线性增加的正弦信号,信号的中心频率为1.501GHz。从图5曲线可以看出,正弦输入信号幅度较低时,增益保持为常数;而随着信号幅度逐渐增大到一定值时,增益迅速下降,表现出压缩特性。利用单音测试方式来观测增益压缩的情况考虑了所有的非线性影响。

图4 在高低两种时钟信号频率设置下增益与本振功率的关系曲线

图5 在高低两种时钟信号频率设置下输入1dB压缩点测量

除了单音测试方式来得到混频器的增益压缩情况,我们还进行了双音测试来测量输入端的三阶交调点。在进行测试时,我们在射频输入端输入叠加的两个正弦信号。其中一个正弦信号的中心频率为1.5010GHz,另外一个正弦信号的中心频率为1.5011GHz。在该测试中,本地振荡信号的中心频率为1.5GHz,此时,混频器输出的中频信号中有两个信号是有用的,其中心频率为分别为两个正弦信号与本地振荡信号的中心频率的差值,较低频的中频信号中心频率为1MHz,较高频的中频信号中心频率为1.1MHz。然而由于系统的非线性,将会产生一些干扰信号,其中由系统的三阶非线性产生的三阶交调项其中心频率分别为0.9MHz和1.2MHz。

图6显示了在两种频率下的输出功率与输入功率的关系曲线,每种频率下的两条曲线分别表示基波和三阶交调项的输入输出功率曲线,其交点所对应的输入功率值为三阶交调点,在高频率设置下,我们获得了高增益,此时系统的三阶交调点的值为7.5 dBm。在低频率设置下,我们以牺牲增益获取较高的线性度,此时系统的三阶交调点的值为11.1dBm。两次的测量结果都是在本地振荡功率为-3.3 dBm条件下进行的。

图6 在高低两种时钟信号频率设置下最大IIP3值测量

图7 在高低两种时钟信号频率设置下噪声系数与频率的关系曲线图

为了较全面地表示混频器的性能,我们用谐波平衡噪声模拟来仿真计算系统的噪声因素。图7显示了在两种频率设置下噪声因素随频带内各频率分量变化的曲线关系。在高频率设置下,噪声因素可达到15.3dB,在低频率设置下,噪声因素为20.6 dB。表示系统在高频时有较好的抗噪声性能。

4 性能总结和分析

表1显示了在高低两种频率设置下的双吉尔伯特混频器的性能总结,同时对参考文献中所提及的其他结构的混频器的性能做了对比。

在参考文献[1]中,作者使用共栅极跨导放大和电流牵引技术,该结构增加了混频器的线性度。文献中所提出的的结构只进行了仿真而没有制作版图测量实际性能,所以只给出了仿真结果。而且,与本文结构不同的是,文献[1]结构中的电感用于电路调谐作用。在参考文献[2]中,作者使用电流牵引技术和片上电感来改善混频器的性能。在这篇文章中,使用了射频CMOS技术来实现更好的模拟电路性能。这两篇文章所提出的的结构所使用的电感都需要一个相对大的基板体积,使得结构非常笨重,不适用于很多对体积有要求的应用中。参考文献[3]和[4]使用了标准的吉尔伯特结构混频器,相对于前两篇文献所提出的结构来说,该结构能够得到一个较高的IIP3值。在参考文献[5]中,一个级联的偶次谐波混频器结构提出,该结构使用感应式匹配网络实现阻抗匹配,以得到更高的性能。文献 [6]提出了使用电荷注入技术的吉尔伯特结构混频器,该结构使用65nm的LP CMOS技术。该结构实现了更高的IIP3性能,当开关对闭合时,IIP3最大值达到了11.1dBm,当开关对断开时,IIP3最大值达到了2.1dBm。文章中利用RC网络构成短路结构来实现高增益,在1.2V的电源电压和5mA电流的损耗下,RC短路网络结构使得增益最高达到10.9dB。总体上来说,本文所提出的的结构在减少功率损耗的同时,比文献[6]获得了一个更高的IIP3值和电压增益。

表1 性能参数总结和比较lt;

全文共6785字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[12270],资料为PDF文档或Word文档,PDF文档可免费转换为Word