英语原文共 5 页,剩余内容已隐藏,支付完成后下载完整资料

FPGA中使用合成热源和温度传感器的硬件微处理器热仿真。

Bartosz Wojciechowski1、Maciej Nikodem1 PawełWeber1,Maciej Zagrabski1 Krzysztof Kępa2

1计算机工程研究所、控制和机器人技术,Wrocław技术大学Wrocław,波兰

美国弗吉尼亚州布莱克斯堡,美国弗吉尼亚理工大学电子与计算机工程布拉德利系。

通讯作者:bartosz.wojciechowski@pwr.edu.pl,电话: 48713202873,传真: 48713202677。

文摘

本文对基于人工热源和温度传感器的基于fpga的硬件热仿真方法进行了初步的评价,该方法可用于实时热模拟基础设施。微处理器的主要功能块被仿真为可控制的加热器,其配置为人为的高功率耗散。基于结构级模拟器的功率输入,调整加热器的功率,并利用基于环形振子的嵌入式热传感器测量其温度。这使得未来的多核微处理器系统能够实时热模拟,考虑到整个冷却系统的长时间常数,以及核心之间的热耦合等效应。

1.背景

当代多核微处理器本质上是温度约束的机器。积极的技术扩展带来了大量的逻辑,只有在线程级的并行执行和导致非常高的功率密度时才能有效地利用这些逻辑。这种高功率密度远远超过了在现代计算机系统中以经济有效的方式消耗的能量。因此,出现了复杂的动态功率/温度管理方案。例如,新的英特尔处理器只有在其温度达到某个预先定义的阈值时才会有完整的性能(所谓的涡轮模式)。因此,热解(散热器)的热容被用于处理突发事件的高性能。

这种系统动力学的热模拟是劳动密集型的,众所周知容易出错[2]。在计算机架构领域,一个错误的来源是过于简化热模型,例如,不承认除主要(通过散热器)以外的温度耗散路径;另一个是不考虑环境温度变化——这主要是由于太短的模拟周期造成的。然而,在需要的时间和计算上,模拟多核系统运行的延长周期是令人望而却步的。目前正积极开展微处理器热模拟研究。例如使用微处理器核心的一个子集来模拟一个基于实际工作负载的通用热地板计划的演变,该计划是在模拟目标系统的其他核心上执行的[3]。

尽管有这些努力,但仍需要模拟基础设施,为长时间内的微处理器热行为提供实时模拟的可能性。为此,我们提出了离散计算的硬件协同仿真环境。用一种具有温度传感器和合成热源的通用FPGA芯片代替了微处理器织物的热流。这种方法允许对动态热管理机制进行实时评估。

在文献[4]中也提出了类似的方法,其中一个微处理器的热性能反映在一个由一系列加热器和温度传感器组成的热测试芯片上。在[4]中提出的热测试芯片由384个热细胞组成,每组有16x24个单元,每个单元的面积为0.05 mm2。每个加热器单元可以在8个电源级别上独立运行。此外,单个细胞的功率输出可以用非常高的频率进行改变。

然而,在FPGA中使用可配置加热器有许多优点,上述解决方案缺乏。首先,使用标准的货架评估板大大降低了这种模拟器的成本。然后,能够重新配置设备,我们提供了更好的灵活性。使用可重构矩阵中实现的加热器,可以更好地控制它们的位置——广泛使用的XUPV5[5]评估板提供了带有8640个可配置块的virtex5设备,其中大多数可以单独配置为加热器。最后,通过对软件栈的小修改,我们可以切换到更新的技术、一个更新的、更大的FPGA设备,或者通过配置一个更小的、带有更低功率的信封的设备来改变模拟设备的热特性。

2.方法

所提出的热仿真系统(TES)由一台PC工作站组成,其中有一个温度感知系统模拟器,该系统模拟器连接到可编程设备(FPGA)外壳上的热仿真器(TE)。PC机上的系统模拟器可以配置各种工作负载。描述在执行过程中程序行为的模型和它的功率耗散的时间分布映射。此外,系统模拟器还可以与其他热模型/模拟器集成在一起,例如热模型的交叉验证热点[6]。

FPGA上的热仿真器由一组人工热源(AHS)组成,它可以模拟微处理器上的功耗元件(见图1),一组温度传感器,以及控制和通信块(CCB),它与PC上的系统模拟器进行通信。在每一步中,从模拟器发送一组新的功耗设置,然后将每个传感器的当前温度发送到PC上。

图1热模拟概念-用加热器和传感器元件替代功能块。

设计中的合成热源利用了环形振荡器(ROs)、移位寄存器、触发器和其他可配置的FPGA矩阵资源。这提供了所需的高功率密度。加热器由基本的加热元件组成,每一个单元的大小都是一个可配置的逻辑块(CLB)[5],它是一个单一的逻辑加热器,由建设银行控制。这种方法为加热器的几何形状提供了很高的灵活性。中国建设银行可以精确控制热源的输出量(默认为3%)。温度传感器是基于ROs的,它演示了温度范围内的二次频率-温度关系,反映了通常使用微处理器(40-110oC)的温度范围。温度传感器上的ROs被设计成能够在单个CLB中提供最小的噪声。建行可以通过RS232或以太网接口与PC通信。使用遗留RS232模块具有低资源消耗的优点。

在FPGA中,多核微处理器的热行为建模方法分为两步。首先,我们对微处理器的热模型进行了识别。通过强迫一组已知的功率刺激,使用一个具有恒定计算强度的能量-病毒式程序,通过读取内置温度传感器,我们获得了处理器的热响应和热模型。在此基础上,我们计算了加热器的位置和大小,使其稳定状态和动态热性能与实际微处理器的性能密切相关。

模拟基础设施要求以脉冲宽度调制(PWM)设置的形式对TE进行功率输入,即加热器处于活动状态的时间百分比。这些值应该基于i)广泛的模拟使用周期精确的模拟器。验证的功率模型,电力性能测量的真实微处理器系统(例如[9,10])。第一种方法是时间和计算的消耗,而后者需要专用的基础设施,并且受到操作系统行为的明显随机性的影响。

3 结果

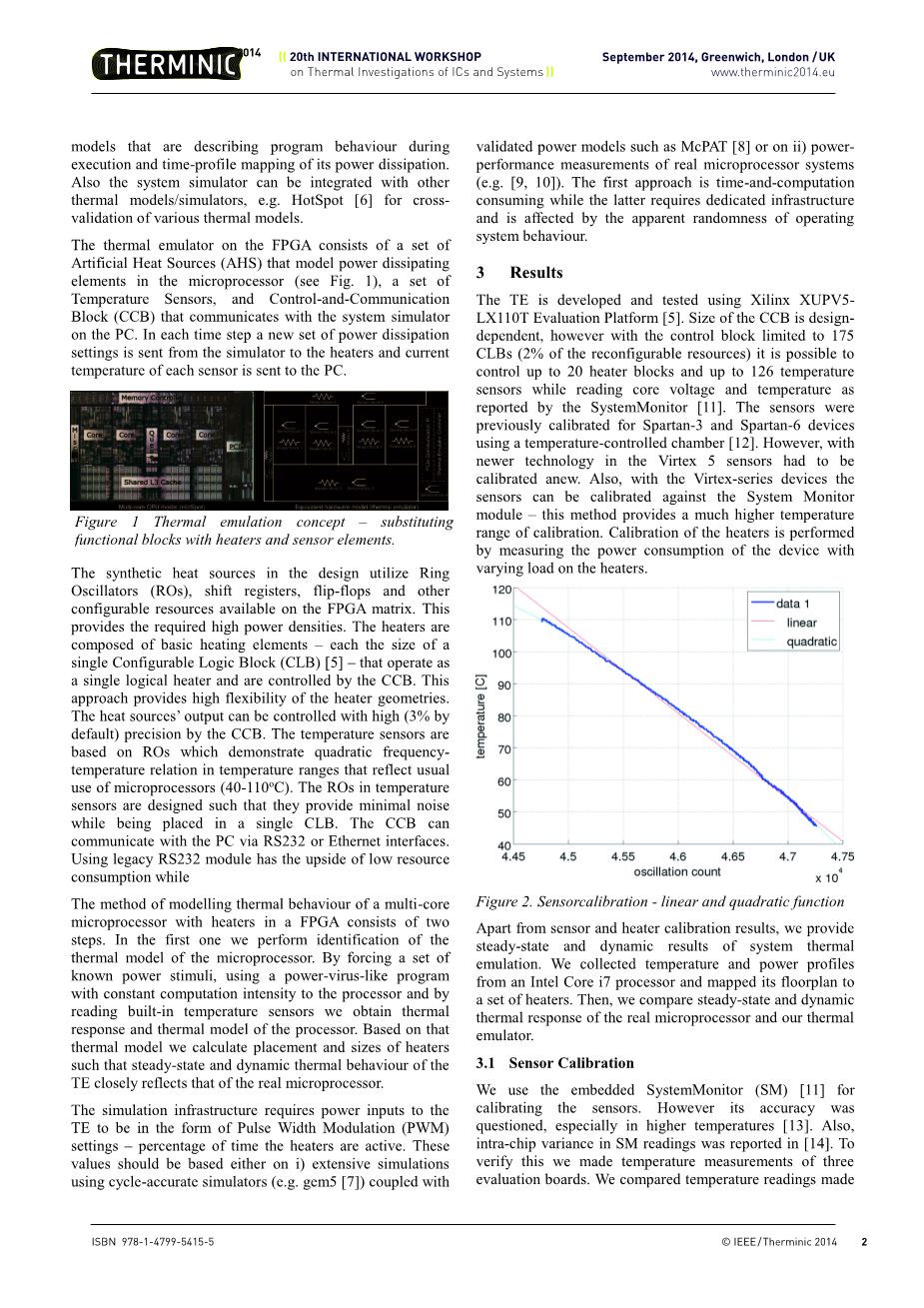

利用Xilinx XUPV5- LX110T评价平台开发和测试TE[5]。建行的规模与设计有关,但控制块限制在175clb(可重构资源的2%),可以控制多达20个加热器模块和多达126个温度传感器,同时读取系统监视器所报告的核心电压和温度[11]。这些传感器以前是用温度控制的房间校准的,用于Spartan-3和Spartan-6设备[12]。然而,随着新的技术在Virtex5传感器必须重新校准。此外,利用virtexseries设备,传感器可以对系统监控模块进行校准的方法提供了更高的校准温度范围。加热器的校准是通过测量在加热器上有不同负载的装置的功耗来完成的。

图2 传感器校准-线性和二次函数。

除了传感器和加热器标定结果外,我们还提供了系统热仿真的稳态和动态结果。我们收集了英特尔酷派i7处理器的温度和功率谱,并将其平面计划映射到一组加热器上。然后比较了实际微处理器和热仿真器的稳态和动态热响应。

3.1 传感器校准

我们使用嵌入式系统监控器(SM)[11]来校准传感器。然而它的准确性受到了质疑,尤其是在高温[13]。此外,在SM读数内的芯片内方差也被报告[14]。为了验证这一点,我们对三个评估板进行了温度测量。我们比较了温度读数。

通过SM和外部传感器使用Pt100 RTD。由系统监测和外部电阻温度计测量的温度分别为3个板的4.5K、6.7K和7.6 K。这可能意味着单个芯片之间传感器读数的微小偏移。

图3由系统监测器(蓝色)和外部电阻温度计(红色)测

量3个不同的评价板和两种不同设计的静态静态温度。

为了校准基于转子的传感器,我们使用了系统监视器的嵌入式温度测量功能。我们在温度范围40- 110 oC的温度范围内,将11个x 11传感器的网络和收集的振荡和温度数据收集起来。为了加热设备,我们使用了一个热空气焊接站——我们在设备的散热片上引导了一股热空气,同时不断地测量温度和系统监控,并记录了传感器网格上的振荡计数。该方法是基于整个片区在升温和冷却过程中是等温的假设。这是预期的,因为散热器具有较高的导热性。该方法优于温度控制室,温度范围与微处理器的正常工作温度密切相关。它使我们的温度范围达到70摄氏度,而整个板不受如此高温的影响。

图4 Intel Core i7 970 6核微处理器的平面布置图。

我们以前的工作是自动校准基于旋转的温度传感器[15],这表明对于Spartan-3和Spartan-6设备,使用线性函数将振荡转化为温度就足够了。然而,对于Virtex-5设备,二次回归必须使用。图2描述这个函数的二次线性逼近。使用二次函数,我们可以将校准误差减小到小于1oC。任何进一步的减少误差都被传感器噪声所禁止,这影响了SM和基于传感器的传感器。

图5一个简化的6核的平面图。

一个典型的现代微处理器的平面布置图如图3所示。我由两组3个核心组成,它们连接到全局共享的L3缓存的一个公共部分。由于微处理器具有高TDP的130 W,它配备了高性能的冷却解决方案:封装和散热。因此,由于硅与散热器之间的热阻较低,热流的主要路径是通过包的顶部。这反映在测量的热行为中(见图6)。当其中一个核心温度升高时,其邻居的温度升高是有限的。另外三组的核心被加热得更少。

在图7和图8中给出了这一情况,给出了6个模拟核的温度分布,并在t=99.9s中利用传感器的11times;11网格建立了FPGA的热图。

3.2加热器控制

对于我们的热仿真器,我们已经评估了在文献中提出的各种加热器设计(例如[14])和w在内部开发。其中包括同步和异步加热器。同步加热器通常会产生较低的功耗,但即使在负载引起的核心压降情况下,其输出也应该相当稳定。此外,它们还需要一个频率源。我们用了两个。

级联DCMs(数字时钟管理器)[5],实现频率为100,200,300和350mhz。我们没有使用更高的频率,因为组成同步加热器的资源有有限的开关时间,并且增加频率较高对电力消耗是有害的。

图6。最初的地面计划是在Virtex5 FPGA中利用模拟核和6个加热器作为仿真微处理器的仿真核心重新创建的。

我们在设计同步加热器时遇到的一个问题是,它们必须额外设计。

当关闭电源时,要小心地使它们不耗散电力。受时钟信号影响的加热器路由的一部分没有被激活信号控制,这导致了加热器关闭后的功率耗散。

图7 测试微处理器6个核心的温度剖面,其中一个核心为100s。

3.3准备的平面布置图

作为第一个利用FPGA的人工加热器进行微处理器热仿真的方法,我们准备了一套与真实微处理器的功率谱相比较的平面布置图。由于只有核心配备了温度传感器,而且它们负责最大的功耗,我们决定只在仿真中反映它们的行为。

在图6中,我们展示了i7处理器中所有6核(c0-c5)的嵌入式热传感器测量的热剖面。在最初的10秒之后,第一个核心(c0)加载了一个热应力程序burnP6。这些测量是通过读取相关的模型特定寄存器(MSR)和时间分辨率为100 ms进行的。为了清晰起见,该概要文件受到了中值滤波——嵌入处理器的传感器受到2oC振幅的干扰。可以立即看到的是温度升高的短尖峰,是来自操作系统的众多后台服务的活动结果。接下来,很容易观察到核心之间的热耦合,即c0核心c1和c3的热耦合比其他三个多。

我们的第一个任务是用加热器的形式来反映相同的静态行为。然而,使用图4所示的平面布置图导致了不同的热剖面。由于FPGA核心与周围环境的热阻较高,模拟核之间的热耦合相当高。因此,为了减少这种效应,我们放置了较小的加热器,并将两组分开。此外,较小的加热器也能使温度的增加与真正的微处理器相比。

图8 模拟6核微处理器的温度分布,具有一个核心活性。

图9 热图与一个仿真的核心活动。

4.结论和未来的工作

该工作提出了一种新的热仿真系统,该系统由一个具有高温度感知的微处理器组成。PC机系统模拟器和FPGA设备中的热仿真器。热仿真器通过对设备物理热流的测量来代替数值计算,方便了实时仿真。该算法为现代多核微处理器动态热管理算法的快速评价提供了依据。

在未来,我们计划将热仿真器与一个高水平的全系统模拟器紧密结合起来,以快速评估多核微处理器的各种动态热管理算法。此外,还计划了一个自动的方法发现和将处理器的动态热模型映射到仿真器。

确认

这项工作得到了波兰国家科学中心(Narodowe Centrum Nauki)的批准。2011/03 / B / ST6/00343。

文学

- Rotem.Efraim等。英特尔微架构的电源管理架构,命名为Sandy Bridge, IEEE Micro(2012): 20-27。

- 弗朗西斯科·贾维尔·梅斯马.马丁尼,埃尔森·k·阿德斯塔尼和何塞·雷诺,描述了处理器热行为的特点,在《关于建筑对编程语言和操作系统的支持的第十五版》中,ASPLOSrsquo;10,第193-204页,纽约,纽约,美国,2010,ACM。

- Beneventi f;Bartolini;Benini,L。“在线热仿真:如何加速你的热控制器设计”,功率和定时建模,优化和仿真(PATMOS), 2013年第23届国际研讨会,vol.,不。2013年9月9日至11日。

- 陈志明,陈志军,等。基于专用集成电路的多核处理器热分析的新方法[j] .北京:清华大学出版社,2003。

-

ML505/M

全文共12824字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[12600],资料为PDF文档或Word文档,PDF文档可免费转换为Word