英语原文共 149 页,剩余内容已隐藏,支付完成后下载完整资料

SDAccel Environment User Guide

SDAccel环境用户指南

UG1023 (v2018.2.xdf) October 2, 2018

Chapter 1

第1章

SDAccel Introduction and Overview

SDAccel简介和概述

The SDAcceltrade; environment provides a framework for developing and delivering FPGA accelerated data center applications using standard programming languages. The SDAccel environment includes a familiar software development flow with an Eclipse-based integrated development environment (IDE), and an architecturally optimizing compiler that makes efficient use of FPGA resources. Developers of accelerated applications will use a familiar software programming work flow to take advantage of FPGA acceleration with little or no prior FPGA or hardware design experience. Acceleration kernel developers can use a hardware-centric approach working through the HLS compiler with standard programming languages to produce a heterogeneous application with both software and hardware components. The software component, or application, is developed in C/C with OpenCLtrade; API calls; the hardware component, or kernel, is developed in C/C , OpenCL, or RTL. The SDAccel environment accommodates various methodologies, allowing developers to start from either the software component or the hardware component.

SDAcceltrade;环境为使用标准编程语言开发和交付FPGA加速数据中心应用程序提供了框架。SDAccel环境包括熟悉的软件开发流程和基于Eclipse的集成开发环境(IDE),以及体系结构优化的编译器,可有效利用FPGA资源。几乎没有或没有先前的FPGA或硬件设计经验的加速应用程序的开发人员将使用熟悉的软件编程工作流程来利用FPGA加速。内核加速开发人员可以使用以硬件为中心的方法,通过HLS编译器使用标准编程语言来生成具有软件和硬件组件的异构应用程序。 软件组件或应用程序是使用OpenCLtrade;API调用在C / C 中开发的; 硬件组件或内核是用C / C ,OpenCL或RTL开发的。 SDAccel环境适用于各种方法,允许开发人员从软件组件或硬件组件开始。

Xilinxreg; FPGAs offer many advantages over traditional CPU/GPU acceleration, including a custom architecture capable of implementing any function that can run on a processor, resulting in better performance at lower power dissipation. To realize the advantages of software acceleration on a Xilinx device, you should look to accelerate large compute-intensive portions of your application in hardware. Implementing these functions in custom hardware lets you achieve an ideal balance between performance and power. The SDAccel environment provides tools and reports to profile the performance of your host application, and determine where the opportunities for acceleration are. The tools also provide automated run-time instrumentation of cache, memory and bus usage to track real-time performance on the hardware.

与传统的CPU / GPU加速相比,Xilinxreg;FPGA具有许多优势,包括能够实现可在处理器上运行的任何功能的定制架构,从而以更低的功耗实现更好的性能。要在Xilinx器件上实现软件加速的优势,你应该在硬件中加速应用程序的那些大型密集型计算的部分。在自定义硬件中实现这些功能可以实现性能和功耗之间的理想平衡。 SDAccel环境提供工具和报告,以分析主机应用程序的性能,并确定加速机会的位置。 这些工具还提供缓存,内存和总线使用的自动运行时检测,以跟踪硬件上的实时性能。

The SDAccel environment targets acceleration hardware platforms such as the Xilinx Alveotrade; U200 and U250 Data Center accelerator cards. These acceleration platforms are designed for computationally intensive applications, specifically applications for live video transcoding, data analytics, and artificial intelligence (AI) applications using machine learning. There are also a number of available third-party acceleration platforms compatible with the SDAccel environment.

SDAccel环境面向加速硬件平台,例如Xilinx Alveotrade;U200和U250数据中心加速卡。 这些加速平台专为计算密集型应用而设计,特别适用于使用机器学习的实时视频转码,数据分析和人工智能(AI)应用。 还有许多可用的第三方加速平台与SDAccel环境兼容。

A growing number of FPGA-accelerated libraries are available through the SDAccel environment, such as the Xilinx Machine Learning (ML) suite to optimize and deploy accelerated ML inference applications. Predefined accelerator functions include targeted applications, such as artificial intelligence, with support for many common machine learning frameworks such as: Caffe, MxNet and TensorFlow; video processing, encryption, and big data analysis. These predefined accelerator libraries offered by Xilinx and third-party developers can be integrated into your accelerated application project quickly to speed development.

通过SDAccel环境可以获得越来越多的FPGA加速库,例如Xilinx机器学习(ML)套件,以优化和部署加速ML推理应用。预定义的加速器功能包括目标应用程序,例如人工智能,支持许多常见的机器学习框架,例如:Caffe,MxNet和TensorFlow; 视频处理,加密和大数据分析。Xilinx和第三方开发人员提供的这些预定义加速器库可以快速集成到你的加速应用程序项目中,以加快开发速度。

Execution Model of an SDAccel Application

SDAccel应用程序的执行模型

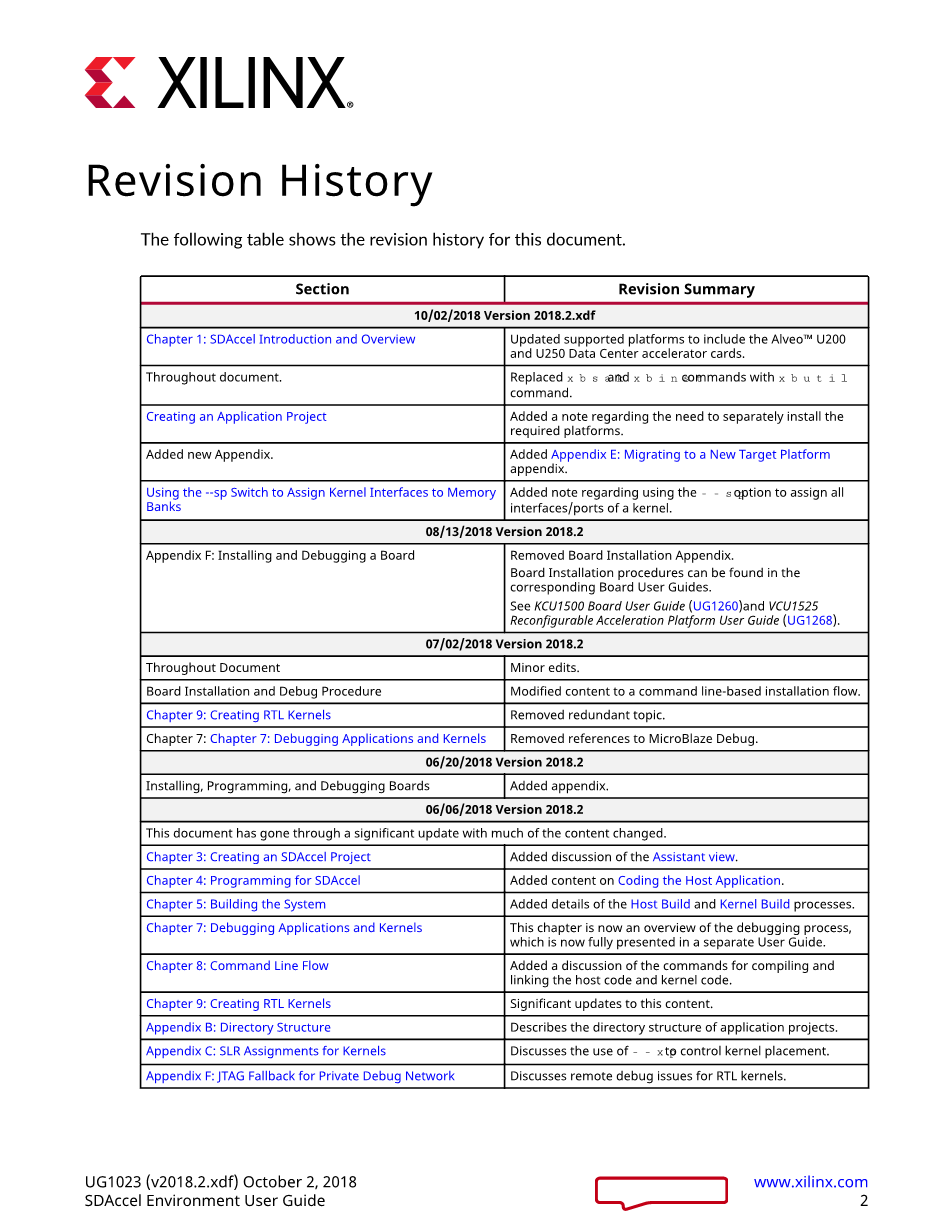

The SDAcceltrade; environment is designed to provide a simplified development experience for FPGA-based software acceleration platforms. The general structure of the SDAccel acceleration platform is shown in the following figure.

SDAcceltrade;环境旨在为基于FPGA的软件加速平台提供简化的开发体验。 SDAccel加速平台的一般结构如下图所示。

Figure 1: Architecture of an SDAccel Application

图1:SDAccel应用程序的体系结构

The custom application is running on the host x86 server and uses OpenCLtrade; API calls to interact with the FPGA accelerators. The SDAccel run time manages those interactions. The application is written in C/C using OpenCL APIs. The custom kernels are running within a Xilinxreg; FPGA through the SDAccel run time that manages interactions between the host application and the accelerator. Communication between the host x86 machine and the SDAccel accelerator board occurs across the PCIereg; bus.

自定义应用程序在主机x86服务器上运行,并使用OpenCLtrade;API调用与FPGA加速器进行交互。 SDAccel运行时管理这些交互。 该应用程序使用OpenCL API以C / C 编写。 定制内核通过SDAccel运行时在Xilinxreg;FPGA中运行,该运行时管理主机应用程序和加速器之间的交互。 主机x86机器和SDAccel加速器板之间的通信发生在PCIereg;总线上。

The SDAccel hardware platform contains global memory banks. The data transfer from the host machine to kernels and from kernels to the host happens through these global memory banks. The kernels running on the FPGA can have one or more memory interfaces. The connection from the memory banks to those memory in

全文共43011字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[133],资料为PDF文档或Word文档,PDF文档可免费转换为Word