英语原文共 13 页,剩余内容已隐藏,支付完成后下载完整资料

采用自动归零功能的低功耗高灵敏度电容式加速度计IC时分复用差分技术

Yan Mei Wang,Pak Kwong Chan,IEEE高级会员,Holden King Ho Li和Soon-Eng Ong

摘 要:本文提出了一种用于电容式加速度计的低功耗高灵敏度开关电容(SC)读出集成电路(IC),其采用体积微细加工技术制造,具有悬臂结构的机械传感器,实现了高灵敏度和低噪音特性。在 SC读出接口中提出了自动调零时间多路复用差分电容——电压转换(AZTMD- -CVC)。CVC基于简单的单端拓扑结构,以产生时分复用差分输出。因此,通过时分复用差分操作,直流偏移,1/f噪声,热漂移和元件失配误差以共模误差的形式显着降低。此外, AZTMD- - CVC 的热噪声通过功率进行分析和优化,以实现良好的噪声功率效率。该应用指定的 IC 芯片采用0.35微米CMOS 技术制造,在plusmn;2.5V电源下的总电流为240mu;A A 。加速度计系统的灵敏度 ty 为1.95 V / g 。该输出噪声功率乘积品质因数(FOM)为 0.28 (mu; g/ Hz )times;mA。

关键词:电容式加速度计,开关电容器电容电压转换器,体积微加工,微机电系统( MEMS )。

1 引言

CAPACITIVE微加速度计具有低漂移、低温度依赖性和低功耗的优点。这种MEMS加速度计在汽车和消费电子产品中越来越流行。诸如惯性等级导航、平台稳定、惯性测量单元(IMU)和微重力测量系统[1]等精密应用需要基于微米级的微加速度传感器。其中一些MEMS加速度计由电池供电,并且通常包含大量的传感接口电路。因此,权力意识是电子读出系统的关键设计优先事项。

比较MEMS加速度计的两种主要微机械加工过程,体微机械加速度计[2]-[4]比表面微机械加速度计[5]-[8]具有更高的灵敏度以及更低的机械热噪声性能、大批量微加工设备。在这项工作中开发的传感器器件是基于悬臂式悬架结构的大体积微加工电容式传感元件。平面外感测方案导致电容灵敏度较高。然而,体微机械感测装置的较高寄生电容是不可避免的。它通过增加与接口电子设备相关的噪声增益因子来影响噪声问题。为了克服这个缺点,设计议程将采用低功耗低噪声电路架构、低噪声放大器设计和噪声功耗优化。通过这种方式,接口电路将能够承受较大的寄生电容,同时提供低噪声性能以及实现低功耗。

2 电容式传感技术综述

在CMOS读出电路中,电荷放大器的直流失调和1/f噪声是限制传感器应用系统中分辨率的主要误差源,特别是在低频带宽(直流到100赫兹)时。斩波稳定(CHS)[9],开关电容自动调零(SC-AZ)[10] [11]和相关双采样(CDS)[12],[13]是公认的电容式感应技术,有效地减少这些错误。与SC方案相比,CHS具有较低的基带噪声水平,因为它不会受到KT/C噪声或热噪声折叠效应的影响。然而,如图1[16]所示,CHS技术对感测节点和地面之间出现的寄生电容敏感。体微机械加工的传感器装置通常具有比其感测电容大至少三至五倍的寄生电容值。这将大大地衰减传感器信号,从而降低分辨率。

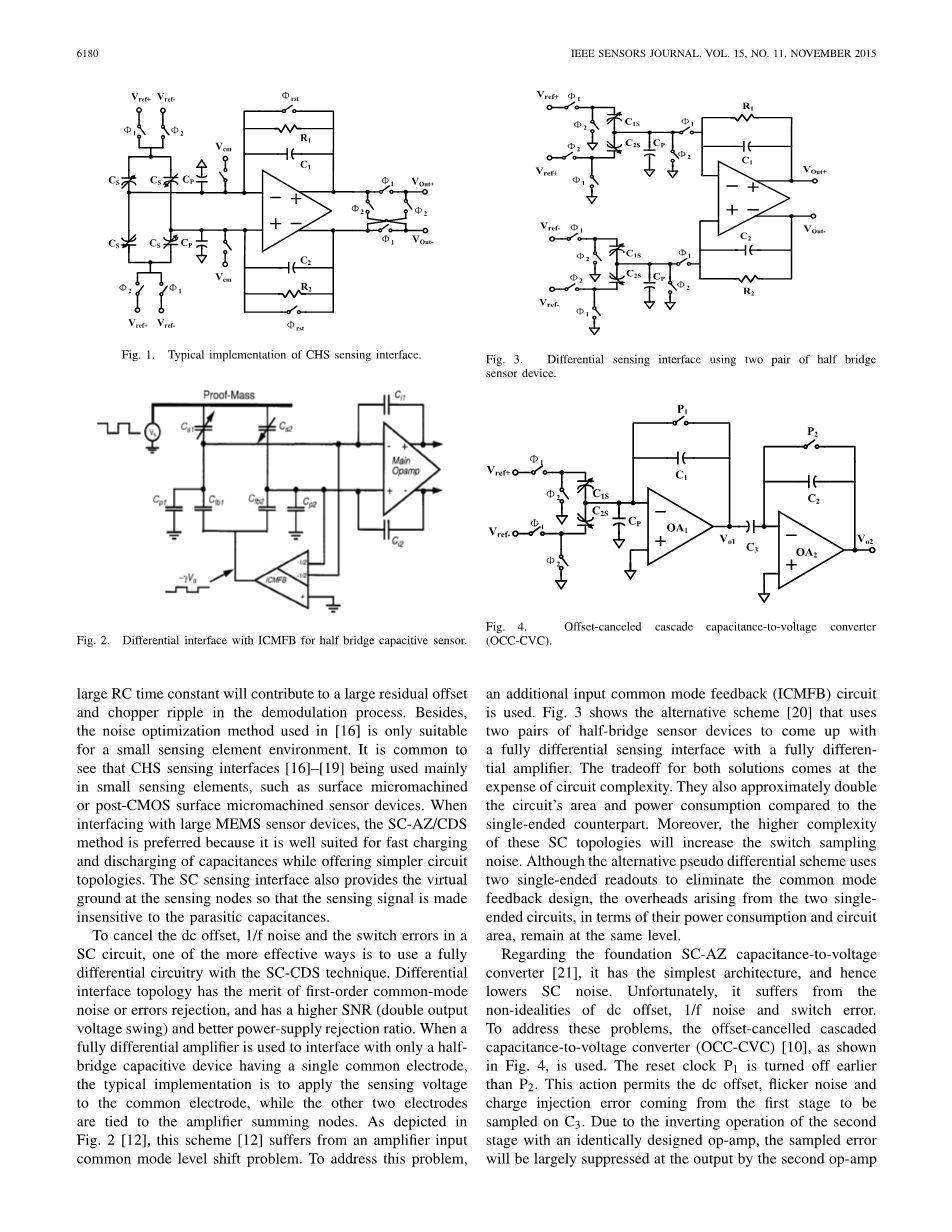

另外,对于传感器电容值为几十pF以上的应用,由电荷注入和时钟馈通效应产生的充电/放电尖峰的幅度可以高达几十mV。在CHS方案中,出现在运算放大器敏感输入端的这些非理想性引起的任何尖峰将在输出端被放大和解调[14],[15]。大交流峰值和较大的RC时间常数会导致解调过程中的残留偏移和斩波纹波较大。此外,[16]中使用的噪声优化方法仅适用于小型传感元件环境。通常CHS传感接口[16] - [19]主要用于小型传感元件,如表面微加工或后CMOS表面微机械传感器设备。当与大型MEMS传感器器件连接时,SC-AZ/CDS方法是首选,因为它非常适合电容的快速充电和放电,同时提供更简单的电路拓扑结构。SC感测接口还在感测节点处提供虚拟接地,使得感测信号对寄生电容不敏感。为了消除SC电路中的直流偏移、1/f噪声和开关误差,更有效的方法之一是使用SC-CDS技术的全差分电路。差分接口拓扑具有一阶共模噪声或误差抑制的优点,并具有较高的SNR(双输出电压摆幅)和更好的电源抑制比。当使用全差分放大器仅与具有单个公共电极的半桥电容器件接合时,典型的实施方式是将感测电压施加到公共电极,而将另外两个电极连接到放大器求和节点。如图2[12]所示,该方案[12]遭受放大器输入共模电平漂移问题。为了解决这个问题,使用额外的输入共模反馈(ICMFB)电路。图3显示了另一种方案[20],它使用两对半桥传感器器件来提供全差分放大器的全差分传感接口。两种解决方案的折衷都是以牺牲电路复杂性为代价的。与单端产品相比,它们的电路面积和功耗也增加了大约两倍。而且,这些SC拓扑结构的较高复杂度将增加开关采样噪声。尽管替代伪差分方案使用两个单端读出来消除共模反馈设计,但两个单端电路在功耗和电路面积方面产生的开销仍然保持在同一水平。

关于SC-AZ电容-电压转换器[21],它具有最简单的结构,因此降低了SC噪声。不幸的是,它受到直流失调,1/f噪声和开关误差的非理想性影响。为了解决这些问题,使用了偏移消除级联电容电压转换器(OCC-CVC)[10],如图4所示。复位时钟P1先于P2关闭。该操作允许在C3上采样来自第一级的直流偏移,闪烁噪声和电荷注入错误。由于第二级采用设计相同的运算放大器进行反相操作,第二级运算放大器的输出端将极大地抑制采样误差具有类似的电路拓扑结构。尽管电路简单,但它依然依赖两个运算放大器,同时不会影响功耗。

在这个SC前端感应接口中,提出了一个自动归零时间复用差分电容-电压转换器(AZTMD-CVC)电路。该电路架构采用简单的单端CVC设计结构提供差分输出。时分复用差分输出提高了信噪比,并降低了低频误差,包括直流失调,1 / f噪声和包括电荷注入和时钟馈通的开关误差,同时不牺牲功耗和电路复杂性。 该方案还避免了对元件匹配的严格要求,并消除了传统全差分接口电路中的共模问题。

最后,在大型传感和寄生电容环境下,前端电荷感应放大器的低噪声设计以及AZTMD-CVC中的噪声功率优化作为解决方案。在介绍之后,第二节描述了与大容量微机械传感器器件相关的电容式传感结构和制造工艺。 第III部分介绍了加速度计IC系统框图和基本构建模块,如AZTMD-CVC及其功率噪声优化设计,SC差分至单端放大器以及电源不敏感的温度补偿振荡器。第四部分讨论了测量结果,随后是第五部分的结束语。

图1. CHS典型的传感接口 图3.使用两对半桥传感器器件的差分传感接口

图2.半桥电容式传感器与ICMFB的差分接口 图4.抵消级联电容电压转换器(OCC- CVC)。

3 散装微机械加速度传感器

图5所示的微机械加速度计装置基于使用批量微加工工艺制造的单梁悬臂梁悬架结构。中心晶片被制成中间移动电极,而上部和下部晶片作为外部固定电极被干燥释放。这三块晶圆通过最佳的气体阻尼和带宽控制融合在一起,同时允许传感元件被封装和气密密封。二氧化硅作为电介质掩埋以隔离这三个电极。 传感器键合焊盘通过多步金属化工艺制成。传感器器件采用引线连接到标准DIP封装,并与PC板上的读出集成电路(IC)一起安装,用于系统集成。

图5.大型微机械加速度传感器装置的横截面图

在此结构中,垂直于检测质量块平面的外部加速度会使检测质量块沿z方向移动,导致检测质量块和两个固定导电电极之间的电容变化。可变电容器C1S和C2S表示差分感测电容,而C1P和C2P是由键合电容构成的寄生电容以及由两个导电电极之间的氧化物绝缘体产生的寄生电容。由于体微机械加工通过选择性地蚀刻整个硅晶片而产生微机械结构,所产生的结构的垂直尺寸可以容易地制造成与500-700mu;m的典型晶片厚度相匹配。具有平面外运动方案的厚检测质量和减少的间隙距离显着提高了传感器设备的电容灵敏度。对于低噪声高分辨率传感器系统设计,传感器应具有高水平的传感灵敏度,以便减轻电子读出电路的增益要求[12],[20],[22]。大型可移动检测质量块还可以减少由质量块的布朗运动引起的机械热噪声,这是限制系统噪声性能的重要因素。表1给出了加速度传感器的规格。

表1加速度传感器规格

4 READOUT接口的体系结构

图6显示加速度计ASIC和电容式传感器装置的简化框图。由于制造工艺的不完善,这种电容式传感器具有不平衡的寄生电容。为了补偿寄生电容C1 P和C2 P之间的差异,实现具有用于平衡差分电容传感器的可编程特征的偏移电容器Cof f set。它可以进行配置,使其可以连接到相应传感电容器的顶部中间位置或中间底部位置。前端接口采用建议的自动调零时间多路复用差分电容电压转换器(AZTMD-CVC)设计,该转换器能够检测传感器电容变化并将其转换为差分输出电压,而无需使用全差电路电压。差分输出耦合到可编程差分到单端SC增益级[23]。然后是信号调理模块,它包含一个外部无源一阶低通滤波器和一个片上低偏移低噪声运算放大器缓冲器。外部无源RC网络对来自SC增益级的准模拟输出提供平滑功能,并定义加速度计IC的带宽。运算放大器缓冲器使用精密放大器拓扑[24]实现。因此,利用级联差分放大器架构将系统偏移最小化,同时使用质心布局策略中的共同质心将随机偏移最小化在大尺寸关键晶体管对上。第三增益阶段确保高增益以最小化增益误差。最后,获得低偏移,低噪声和高CMRR性能指标。此外,与控制时钟逻辑结合的低功耗不受电源影响的温度补偿张弛振荡器将生成SC系统的控制时钟。

图6.电容式加速度计IC的简化框图

A. AZTMD-CVC的操作原理

图7描述了自动调零时间复用差分电容-电压转换器(AZTMD-CVC)及其时分复用制时钟信号。与运算放大器OA1的正输入端串联的非理想电压源Vof f表示运算放大器的闪烁噪声和直流偏移误差。该结构处理多速率SC设计。等于主时钟频率的重置时钟1被设计为多路复用时钟频率的两倍,包括电荷转移时钟T1,T2和用于时分多路复用差分通道的相应重置周期。

图7. AZTMD-CVC及其控制时钟的示意图

B. 差分至单端可编程SC增益放大器

AZTMD-CVC的无源S / H输出将连接到SC放大器,用于缩放感应信号。图8描述了SC-CDS差分-单端可编程增益级及其控制时钟的示意图。一个5位可编程电容阵列(PCA)可实现与反馈电容器C2和C 2t 并联。这个允许调整第二电压增益级,以便它可以补偿来自传感器装置的增益变化。由于信号耦合是基于无源电容元件的,所以电容器Ch1(如图4所示)和C1之间会发生电荷共享效应。

图8.相对于复位时钟1其控制时钟的差分至单端可编程SC-CDS增益级的示意图

C. 电子噪声分析和优化

整个系统噪声性能指标的特征在于由传感器的布朗噪声等效加速(BNEA)和电路噪声等效值确定的总噪声等效加速度(TNEA加速(CNEA)。在这种设计中,体积微加工传感器的副作用达到了低布朗噪声水平低于1微克/赫兹,使得C NEA是整个系统噪音水平的限制因素。对于平衡设计,电子系统中的噪声和功耗之间总是存在折衷。较低的电路噪声通常需要较高的功耗,反之亦然。因此,有必要检查关于SC CVC的输出噪声PSD关于功耗的关键参数。由于接口电路中使用的加速度计检测电容和积分电容都很大,所以KT/C噪声相对于放大器可以忽略不计,包括1/f噪声和宽带热噪声的噪声。如A部分所解释,放大器偏移和1/f闪烁噪声可以视为共模误差。它们可以在时分多路复用差分电压输出端被消除,从而使宽带热噪声成为主导接口电路中的噪声因子。因此,热噪声功耗优化成为低噪声前端电子接口的主要设计策略。图9描述了基于推挽电流镜的操作(AZTMD-CVC)中的跨导放大器(OTA)拓扑[25]。根据电流镜像晶体管中的电流比率设置,绘制总电流It

全文共11032字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[15454],资料为PDF文档或Word文档,PDF文档可免费转换为Word