英语原文共 11 页,剩余内容已隐藏,支付完成后下载完整资料

基于fpga的永磁同步电机速度控制芯片驱动与自适应模糊控制

摘要

新一代的现场可编程门,(FPGA)技术实现了嵌入式处理器智能,属性(IP)和要集成应用程序IP 可编程芯片系统(SoPC)开发环境。 因此,在这种SoPC环境下,本研究提出一种速度控制集成电路 (IC)用于永磁同步电机(PMSM)驱动。首先,数学模型定义了永磁同步电机,并在电流环中使用矢量控制 介绍了永磁同步电机的驱动。然后是自适应模糊控制器 用于处理动态不确定性和外部载荷 提出了永磁同步电机调速回路的影响。在那之后,一个 设计了基于fpga的速度控制芯片来实现控制器。 提出的速度控制IC有两个IP,一个Nios II嵌入式 处理器IP和应用程序IP。Nios II处理器是 用于开发软件中的自适应模糊控制器 控制算法复杂,采样频率低 控制(速度控制:2khz)。设计的应用程序IP为 在硬件上实现了电流矢量控制器 由于需要高采样频率控制 (电流回路:16khz,脉宽调制电路:4 - 8mhz) 但简单的计算。最后,建立了实验系统 并给出了实验结果。

索引术语-现场可编程门阵列(FPGAs),模糊 控制,永磁电机,同步电机驱动, 可编程芯片系统(SoPC)。

1介绍

由于优越的功率密度的优势,高性能的运动控制-快速响应并具有较好的精度,永磁同步电机在许多自动化控制领域中都有广泛的应用致动器[1]。但是在工业应用中,有很多不确定性,比如系统参数的不确定性,外部负载扰动、摩擦力、未建模的不确定性等总是降低性能质量的预设计电机驱动系统。为了解决这个问题,最近多年来,许多智能控制技术如[2]-[5]等模糊控制,神经网络控制,自适应模糊控制以及其它控制方法,已被开发并应用于伺服电机的速度控制,以获得高的运行的性能。高性能的电机控制系统应该对其控制的调整有快速的动态响应参数,使电机输出受到扰动的影响能否尽快恢复到原来的状态[6]。不过,执行神经网络还是自适应的模糊控制需要大量的计算,因此需要实现这些高度复杂的控制算法依赖于PC机系统在大多数研究[3],[7]。近年来,定点数字信号处理器(DSP)和现场可编程门阵列(FPGA)也提供了一可能的解决方案[8],[9]。与FPGA相比,虽然上述采用DSP的智能控制技术提供了一种灵活的控制方式技术,它经历了一个漫长的发展过程和浪费过程许多CPU资源[9]。

如今,由于超大规模集成电路技术的进步FPGA已经引起了更多的关注。的优点FPGA采用可编程的硬线特性,速度快上市时间短,设计周期短,内置处理器,低功耗,高密度实现数字系统[10]的。FPGA提供了一种折衷方案之间的专用应用程序指定集成电路(ASIC)硬件和通用处理器[11]。因此,在逆变器[12],[13]和许多实际应用对电机控制[9]、[14]-[17]进行了研究。Tzou [12]和周[13]分别给出了一个FPGA的实现三相空间矢量脉宽调制(PWM)逆变器。周[9]提出了一种速度fpga实现永磁同步电机伺服控制器。速度采用PI控制器永磁同步电机驱动回路。Takshashi[14]利用FPGA实现一个完整的交流伺服控制器。一个特定于应用程序的标准产品(ASSP)的创建是为了减少门计数本研究考虑。Fang[16]采用了基于fpga的方式芯片设计了滑模控制的概念核心永磁同步电动机的策略。Lin[17]提出了一种模糊滑模基于FPGA的直线感应电机驱动控制。的具有模糊推理机制的模糊滑模控制器提出了实时适应系统不确定性的方法这篇论文。但是,以上的研究都是针对伺服的逆变器或交流电机控制系统仅采用FPGA硬件用简单的算法实现。

嵌入式处理器IP和应用IP现在可以了开发并下载到FPGA中进行构造一个基于可编程芯片的系统(SoPC)环境[18] -[20],允许用户设计一个SoPC模块在一个FPGA芯片中混合硬件和软件。的电路要求处理速度快,但计算简单适用于FPGA的硬件实现控制算法复杂,计算量大可以通过软件在FPGA上实现。结果是软硬件协同设计功能,增加可编程性,设计的数字系统灵活性降低提高了系统的开发时间和性能。我们之前的工作[21]-[23]已经成功的应用于SoPC技术在永磁同步电机驱动、机器人伺服系统中的机器手臂和电动缸。

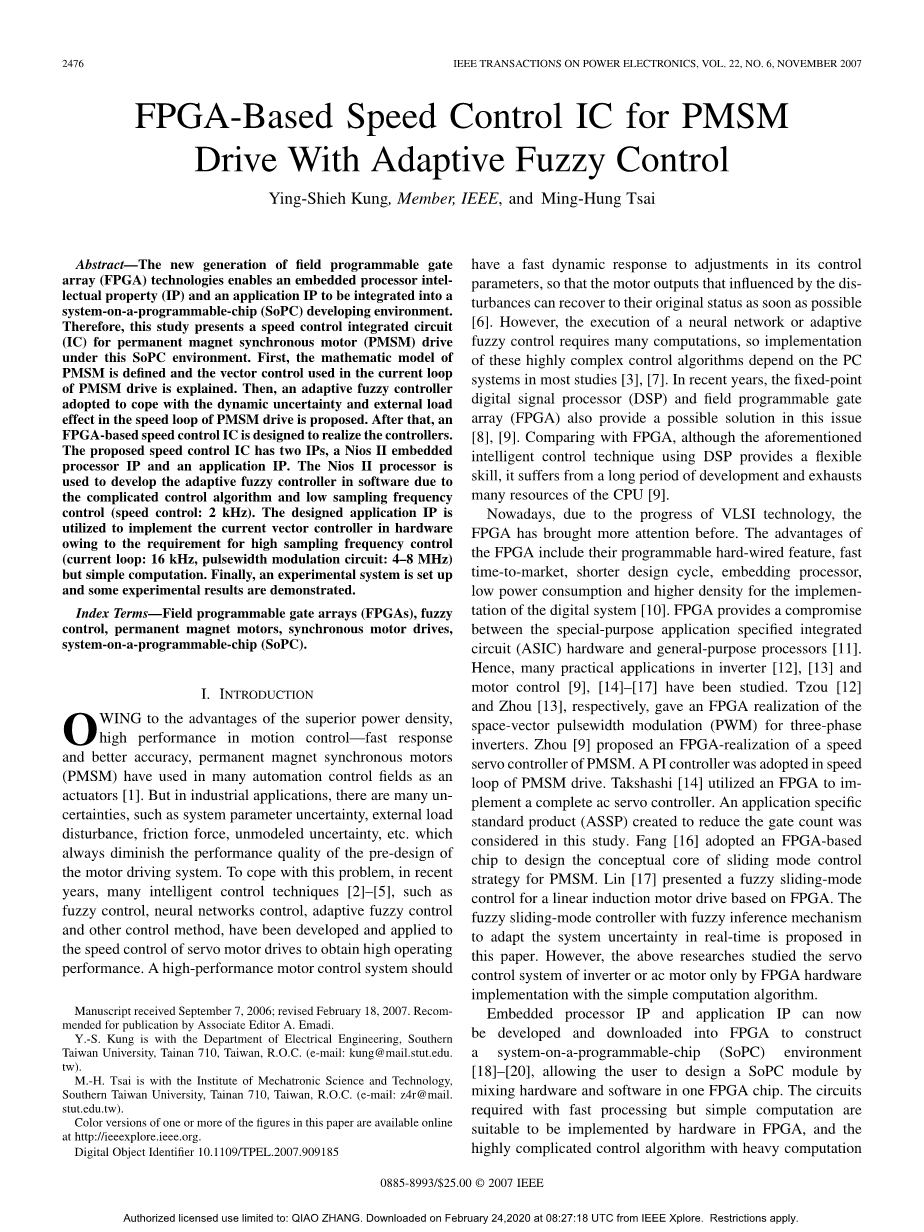

为了充分利用这些优势,本研究提出了一种全数字化的解决方案基于单片机的永磁同步电机调速集成电路新一代FPGA技术,如图1所示。被提议的运动控制IC有两个IPs,一个Nios II嵌入式处理器IP和应用程序IP。Nios嵌入式处理器采用IP实现自适应模糊控制功能采用软件实现,并利用应用IP实现电流用硬件进行矢量控制。此外,一个有限状态机还考虑了用有限状态机(FSM)方法来减少逻辑元素(LEs)本文中FPGA的使用。因此,所有功能,哪些是基于软硬件协同设计的,需要哪些建立一个完整的数字伺服控制的永磁同步电机驱动可以集成在一个FPGA芯片。本文使用的FPGA芯片是带有2060个LEs,最大301的Altera气旋EP1C20吗用户I/O引脚,294 912 b的RAM,和一个Nios II嵌入式处理器。处理器有一个32-b可配置的CPU核心,16米字节闪存,1m字节SRAM和16m字节SDRAM。最后,通过FPGA实现了一个实验系统板,一个逆变器和一个永磁同步电机,是用来验证的基于fpga的速度控制的正确性和有效性Ic。

2永磁电动机伺服系统描述及数学模型

基于fpga的伺服系统的内部结构永磁同步电机驱动系统如图1所示。自适应利用软件开发了速度环模糊控制Nios II嵌入式处理器。电流矢量控制基于FPGA的硬件实现了永磁同步电机的设计方案的详细的理论描述如下:

永磁同步电动机的数学模型介绍了典型永磁同步电动机的数学模型d-q二轴同步旋转参考系,如下图所示[1]:

其中VD为轴向电压;是VQ轴电流,R是相绕组电阻;LD,LQ是轴电感;we为电角速度;^f是永磁体磁链。a的当前控件永磁同步电机的驱动是基于矢量控制的方法,如中频在图1中控制为0,对永磁同步电机进行解耦。因此,开发的电磁转矩可简化为[1]

考虑机械负载,永磁同步电动机的动态方程为[1]

其中p,w,t,k,j,b,TL和分别为摆数、转子转速、电机转矩、转矩常数、惯量、阻尼和转矩。

图1展示了永磁同步电机的电流回路,包括两个PI控制器,Clark坐标变换,改进的逆变器,Park,逆变器,SVPWM,编码器的脉冲信号检测和其他元件。矢量控制(在图中设置为0)。1)在永磁同步电机的电流环中,对永磁同步电机的非线性和耦合特性进行解耦。因此,控制永磁同步电机的转矩只需要控制电流的方向。给出了静止坐标系a与静止坐标系a之间的变换公式

图1所示为永磁同步电机驱动的自适应模糊控制器的结构。它由一个控制器、一个控制器和一个调节器组成。1)模糊控制器:一般来说,与模糊系统串联的P控制器属于PD型模糊控制器,而与模糊系统串联的PI控制器属于PID型模糊控制器,我们所设计的系统如图1所示。后者的一个与前一种方法相比,具有更大的灵活性和更少的稳态误差。该模糊控制器采用单模糊器、三角隶属函数、乘积推理规则和中心平均去模糊器方法。在图1中,跟踪误差和误差变化定义为

1)以Ke, e, Kde和作为模糊控制器的输入和输出变量,基于对称三角隶属函数定义其语言值{A1,A2,E}

其中xi为输入值;em为输出值;xi,wi为三角形函数的均值和宽度;ke为误差增益和kde误差变化量。

- 通过参考dy-namic响应特性[4]来选择初始模糊控制规则,针对每个数组值{A1,A2,E}。设计了7个模糊集,并针对两个输入和一个输出的模糊系统设计了49个模糊控制规则。因此,是(13)中的49。

- 利用辛-格列通模糊度法、产品推理法、中心平均模糊度法建立模糊系统。因此,(13)用下式代替:[25]

c1,c2,cm参数可调。在简化中,每个参数cm的可调范围限制cm min和cm max之间。

参考模型:以图1中自适应模糊控制器中的二阶系统为参考模型,可表示为

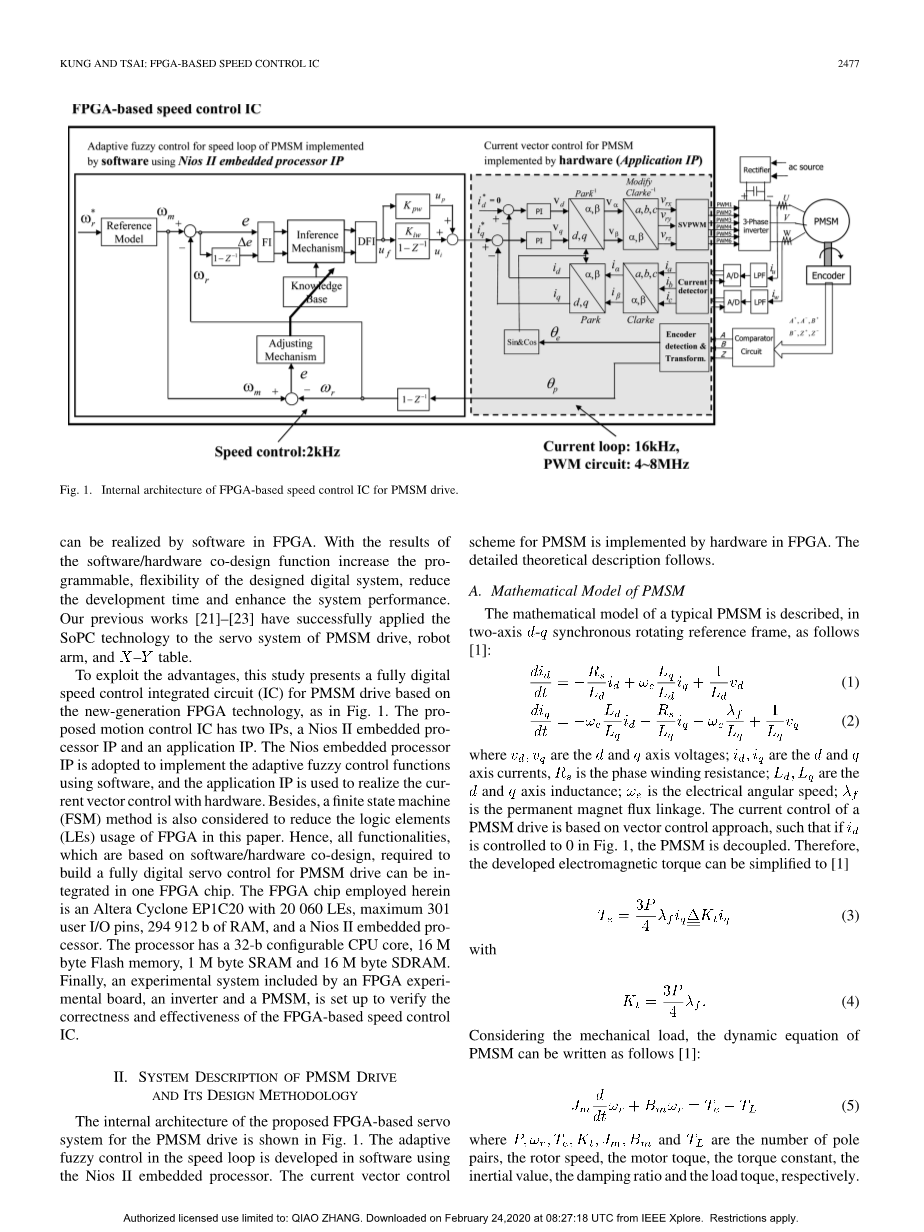

Fig5 利用FSM方法设计了如图2所示的CCCT电路

利用双线性变换,连续模型

可由

后移算子转化为离散模型,且为离散模型的参数。参数调节机制:采用梯度下降法推导出图1所示的模糊控制律。对模糊控制器的参数进行调整的主要目的是在调整转速和输出转速的基础上最小化平方误差(瞬时成本函数)。瞬时成本函数由式

并对其参数进行了相应的调整

其中a表示学习率。Cj的参数调整,最初,假设TL为零(5),并采取Laplace变换(3)和(5)

接下来,使用双线性变换推导出永磁同步电动机驱动系统方程,源于下式子

其中为z-1二次变换算子,T为振幅周期。另外,在图1中,电流指令由模糊控制器的输出IQ*来表示

表示其中Kpw,Kiw为PI控制器的增益,ui为控制器的输出。

用链式法则重写,可将偏微分方程(18)改写为

将式(25)和式(26)代入式(24)和式(19),则式(14)所描述的模糊控制器参数可由下式调整

由于电机参数B不易确定,所以(27)用了(B)这个符号。这两者是一致的B是实际值,而(B)代表运算符号。

4提出一种基于fpga的永磁同步电机驱动控制芯片

图2给出了基于fpga的永磁同步电机驱动速度控制芯片的内部结构。基于SoPC技术,设计了速度控制芯片,该芯片由Nios II嵌入式处理器IP和应用IP组成,由ALTERA公司发展。

本文采用的FPGA芯片为骤风EP1C20,其容量为20060 LEs,最多支持301个io口和294912b的RAM。NIOS 2嵌入式处理器有一个32-b可配置的CPUcore, 16 M字节的闪存,1 M字节的SRAM和16 M字节的SDRAM。自定义软件开发工具包(SDK)由用于SoPCdesign的已编译的软件例程库、用于重新构建库的Make-file和用于每个外设的包含结构的C头文件组成。TheNios II处理器的IP地址IP 如图二用于在永磁同步电机驱动软件的速度环中实现了自适应模糊控制。Nios II处理器的时钟频率为50 MHz。图3给出了自适应模糊控制的主程序和中断服务例程(ISR)的流程图,其中中断间隔设计为500us。所有程序都是用C语言编写的,如图3所示。然后,通过Nios I (IDE)中的编译器和链接器操作,生成并可下载到外部Flash 或者基于JTAG接口的SDRAM。最后,这个执行代码可以由Nios II处理器IP通过图2中的总线接口读取。在Nios II处理器中执行速度环自适应模糊控制算法的计算时间为120秒。利用theC语言开发的控制算法不仅具有可移植性的优点,而且易于实现成熟代码的移植。它已经在其他设备(如DSP或基于pc的系统)到Nios II处理器上得到了很好的开发。

硬件实现的应用IP,如图所示。2、采用PMSM伺服实现电流矢量控制。此外,它的电路包括分频器、电流控制器和坐标变换(CCCT)、QEP检测和变换、ADC读输入和变换等。电流控制的采样频率为16khz。设计的FPGA控制器的工作时钟频率为50mhz,分频器产生50mhz (Clk)、25mhz (Clk-sp)和16khz (Clk-ctr)时钟,为图2中应用IP的所有模块电路供电。图2中CCCT的内部电路执行两个PI控制器的功能,查找函数表,并对Clark、Park、反Park、经过修改的反Clarke进行坐标变换。然而,这些公式的计算量很大。本文介绍了两种设计方法,一种是并行处理方法,另一种是有限状态机方法。在前一种方法中,所设计的CCCT电路如图4所示,即-轴PI控制器、-axisPI控制器、Clarke、Park、反 Park等电路连续、同时工作。如图四4、数据类型为12字长, Q11格式,2的补码操作。PI控制器的每个电路包括三个加法器、两个倍增器和两个d型触发器。公园或逆公园转换电路还需要两个加法器和四个乘法器。在这种设计方法下,CCCT循环的资源使用需要3659个逻辑元件(LEs)和24576个RAM位,如表I(a)的灰色部分所示。虽然并行处理方法具有较快的计算能力,但也消耗了较多的FPGA资源。为了减少FPGA的资源占用,提出了采用FSM方法设计的CCCT电路,如图5所示一个加法器,一个乘法器,一个1-b左移器,一个查找表并操作23步机进行了全面的实现。CCCT的计算见图2。

图5中的数据类型为12-b长度和Q11格式。在图5中,步骤s0-s1用于三角函数查找表;计算步骤s2-s4和s5-s7d轴PI控制器,q轴PI控制器;s8-s12和步骤,s13-s16, s16-s18, s19-s23表示变换逆park,修正逆clark,clark,park。在图5中,FPGA中每一步的操作可在40纳秒(25兆赫时钟)内完成;因此总共23步需要0.92 s的操作时间。虽然FSM方法比并行处理需要更多的操作时间方法在执行CCCT电路时,不丢失任何控制性能在整个系统因为0.92 s操作时间远远小于设计的采样间隔62.5 s(16 kHz)的电流控制回路,如图2所示。此外,从表I(b)的灰色填充部分,表示资源用FSM方法设计的CCCT电路的使用频率为864 LEs和24576 RAM b;因此,FSM方法,比较使用并行处理方法,只花费1/4的时间FPGA中的资源使用(LEs)。除了CCCT图2中的电路,还有SVPWM、QEP等电路设计分别如图6(a)和(b)所示的空间电路设计为16khz频率和1us的死区

FPGA中SVPWM电路的相关设计方法是指[12]。最后,FPGA的速度控制IC的实用程序如图2所示计算结果列在表i中控制器结构的使用,其中有C

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[237301],资料为PDF文档或Word文档,PDF文档可免费转换为Word