英语原文共 14 页,剩余内容已隐藏,支付完成后下载完整资料

解决全桥单级PFC的技术问题摘要

AC-DC变换具有功率因数校正使用全桥单级(FBSS)转换器可能会引入各种复杂的操作限制和不经常在文献里描述到的控制问题。这个问题主要是因为这一事实,即他们低估,并限制这些应用程序的数量拓扑。这些问题被标识为变压器初级饱和度和输出电压扰动。轻负载时的操作和随着宽负载范围变化,也是一个复杂的问题导致无法控制的输入电流和直流母线电压。这个论文阐明了类似涉及到在FBSS拓扑操作影响的技术问题,并提出设计标准和控制解决方案,以减少它们的影响。一个低成本的续流电路(FWC)允许空的输入电流来解决轻负载操作问题也提出了。

关键词:续流回路(FWC),全桥单级(FBSS),全桥单级转换器,输出电压

扰动,功率因数控制器(PFC),初级变压器饱和。

1.引言

为了符合标准,IEC1000-3-2,现代开关模式电源的输入电流(SMPS)必须是几乎正弦的。此特性可使用附加的AC-DC转换器的输入来实现,该转换器调节正弦输入电流和输出电压为一个大于电源电压峰值的直流值。对于低功耗应用,不到500瓦,一个升压转换器,图1(a),或者两个并联的输入升压到更高的功率等级,图1(b),是经常使用的。然而,这些两级功率应用呈现众所周知的缺点,即:成本高和具有在每一个阶段非常高的效率的必要性。使用高性能无桥方法图1(c)和(d)提高效率是可能的,但是成本总是会影响。

图1显示了全桥两级,用于执行正弦输入的开关模式功率应用的全体。

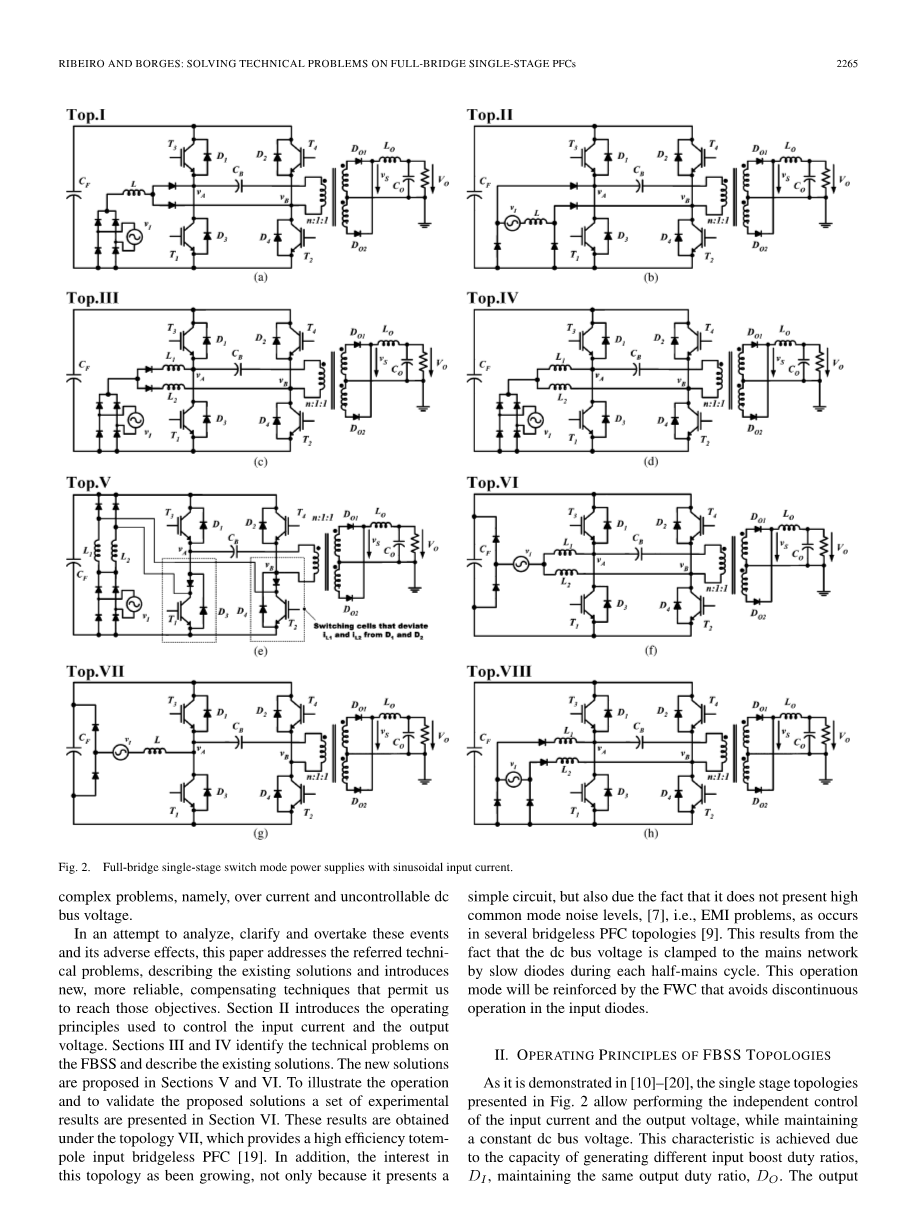

为了解决以上问题,各种FBSS拓扑结构被提出,见图2. 实验提出的结果证明,它是能够实现两个参与转换器操作转换过程(调控输出电压和输入电流限制)的同时提供高效率和低输入电流总谐波失真。独立于这一事实,FBSS拓扑呈现不同的,通常情况下,既没有被分析,也没有提到的技术问题,因为它们低估和限制这些转换器的应用的数量。

FBSS的问题与电流在每个桥的腿的中间点的注入相关,使输出电压扰动和初级变压器饱和。在轻负载运行和宽负载变化发生的可能性,10%和90%之间,也会导致复杂的问题,即:过电流和不可控的直流母线电压。

在试图进行分析,澄清和超越这些事故及其不利影响,本文记述了相关的技术问题,描述了现有解决方案和介绍新的,更可靠,补偿技术,使我们要达到这些目标。第二部分介绍了用于控制输入电流和输出电压的操作原则。第三和第四部分确认了关于FBSS的技术问题和描述了存在的解决方法。新的解决方法在第五和第六部分提出。为了解释操作和验证提出的解决方法,一系列的试验结果将在第七部分呈现。这些结果在拓扑七是可以达到的,它提供了一个高效率的图腾柱下无桥输入PFC。此外,对于这种拓扑结构额兴趣一直在增长,这不仅是因为它提出了一个简单的电路,而且还由于它不存在高共模噪声水平这一事实。EMI问题,也在若干无桥PFC拓扑中发生。这个来自于这一事实,即直流母线电压在每个半干线循环期间通过缓慢二极管被钳位到电源网络。此操作模式将由FWC被加强,避免在输入二极管的不连续操作。

2. FBSS拓扑的工作原理

就像在[10]–[20]中解释的,图2中的单级拓扑允许执行输入电流和输出电压的独立控制,同时维持的一个恒定的直流母线电压。这个特性被实现是因为产生不同的输入升压占空比的能力,DI,保持相同的输出占空比,DO。输出的占空比,DO,由输出电压调节器施加,因此,不能为了控制输入电流波形而改变。输入占空比DI由选择适当状态S00或者S11输入电流控时器获得,在vP = 0的时间间隙,为了提供输入电流波形。这个事实介绍了DI的一个限制,考虑到的变化范围,DI的变化范围直接来自于DO。

DI min = DO

DI max = 1 for Top. I (1)

DI min = DO/2

DI max =( 1minus; DO)/2 for Tops. II to VIII. (2)

考虑到拓扑7,如图3,表明保持输出恒压的同时控制输入电流是可能的。图3也包括了不同功率晶体管开关状态,S00, S01, S10, S11。图3中,TS和TSO是初级和整流次级电压的开关周期,分别为,n为变压器匝数比和VG1到VG4的晶体管栅极信号。恒定的直流母线电压,确保在VI = VI max,输入升压有能力产生正和负的平均电流的斜坡,是可以得到的。这个条件描述了最小的VCF的值,取决于VI max和 DO

VCF gt;VI max/ (1 minus; DI min ) hArr;VCF gt;VI max/(1 – DO ) for Top. I (3)

VCF gt;VI max/(1 minus; DI min) hArr;VCF gt;2VI max/(2 – DO) for Tops. II to VIII. (4)

根据在[18] 和 [19]中说明的关于输出占空比的最大值的设计标准。DOmax的实现考虑到的比例,输入电路的最大CCM角度alpha;max,和一个VCF安全边缘,pCF[角区间[alpha;max, theta;]是可以被忽略的如果L被设计是考虑到PI min(CCM) gt; 0.1。POmax,见图4和(9)]

DOmax =2/{(VI max/VI min) ・ [(pCF 1)/ sin(alpha;max)] 1} (5)

图4表现了典型的平均输入电流演化,<iI>TS,在拓扑2到8中实现为电源的半周期电压。在拓扑1,因为这个事实,即它允许它允许DI max =1,角度alpha;为零且输入电流开始严格来源参考,因为omega;t=0。在图 4角度beta;对应于输入电流的CCM和DCM之间的过渡角。

3. 输出电压扰动和初级变压器饱和

A.输出电压扰动

各种FBSS拓扑的输出电压纹波首次提出在[19]而且电压扰动的发生在该出版物也被认定。输出电压扰动结果直接来源于初级变压器在延迟时间间隔期间td发生的电压扰动。在这段时间间隔中,只有一个功率晶体管是接通,因此,在主变压器电压级是由在桥腿中点注入的电流决定的。(初级电流,iP,和电感器电流iL1和iL2)。

变压器初级电压扰动的发生在图中所示的死区时间。图5(a)和(b)示出了即存在两个可能的桥状态(S00,S01,S10,S11-桥状态),当仅晶体管T1接通。

每个状态的定义取决于初级电流,IP和电感的电流之间,IL1和IL2的关系,产生了,这样一来,被称为扰动。例如,图6(a)表示典型的输出电压纹波波形,其中100赫兹分量和输出电压可见(在有输出750瓦的功率的拓扑6中得到)。

图6中表现的输出电压扰动不损害大多数负载是个事实,但是它的存在表明初级电压没有零平均值,这可能导致初级变压器饱和。这些扰动还可能会带来更高的振幅值,考虑到设计参数等的影响:死区时间间隔,td;输出滤波元件值,LO和CO;输入电感的电流纹波;并且,最后,所采用的输出电压控制器。这些方面表明调查并找到解决可能减轻这些情况的办法是多么重要。

B. 初级互感器饱和

比输出电压扰动更成问题的是励磁电流扰动,ILM,而表现了一种速度更快动态然后输出电压。励磁电流扰动和输出电压扰动有相同的原因,即是由于变压器在死区时间发生的初级电压扰动。图6(b)示出了由于变压器初级电压扰动发生的核心饱和和图6(c)示出了磁化电流与输入电流相关的演化。当饱和发生时,励磁电感表现是短路点路和电流只被绕组电阻限制。除了一些重要的情况下,饱和通常降低的时间间隔期间发生时,作为由功率晶体管的支持的电流的过量。 然而,效率,因此,会总是相当大的影响。

虽然随着饱和发生的概率较小,单级的DC-DC转换器桥已经遭受了这个问题,由于存在于功率晶体管传导电压的小差异。通常情况下,有必要使用隔离变压器具有相当安全的安全余量DC模块电容的磁化电流与主变压器串联,以避免饱和,CB。在在FBSS拓扑,这些解决方案可能是不够的,由于到主电压扰动的幅值较高。下一节介绍已经被开发和测试的一些可用的解决方案,为了避免输出测试电压扰动和主变压器饱和。

C.可行的解决方法

为了解决所提问题,开关单元,图2(e)可以使用(请注意,拓扑5对应于确定的两个偏离电流电路在图中的拓扑4)。这些单元中的初级电流,IP,是唯一在死区时间注入桥腿的,因此,初级电压扰动呈现对称行为避免,这种方式,生成的输出电压扰动和变压器饱和。该在提出的结果[19]表明,该电路具有良好的表现在输

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[148479],资料为PDF文档或Word文档,PDF文档可免费转换为Word