用于IEC 61499功能块的VHDL体系结构

摘要:迄今为止,IEC 61499运行时系统专注于部署到各种微处理器的软件实现。本研究提出了一种新颖且可行的架构,允许在现场可编程门阵列(FPGA)中将IEC 61499模型展开为定制逻辑。作者开发了一个编译器/转换器,能够将IEC 61499模型转换为符合该体系结构的等效的超高速集成电路(VHSIC)硬件描述语言(VHDL)。这种体系结构以及相关的编译器/转换器可以帮助您深入了解IEC 61499元素在FPGA环境中的运行时行为。本研究还报告了在特定测试场景中执行的案例研究,以确定所描述架构和相关编译器/译码器的适用性和性能。因此,发现将IEC 61499模型部署到FPGA允许利用FPGA的并行执行能力,从而能够处理同时事件并且并行执行算法。还发现对该体系结构的简单修改导致更传统的顺序行为。此外,该架构还能够提供IEC 61499模型的高度确定性的硬实时实现。

1 介绍

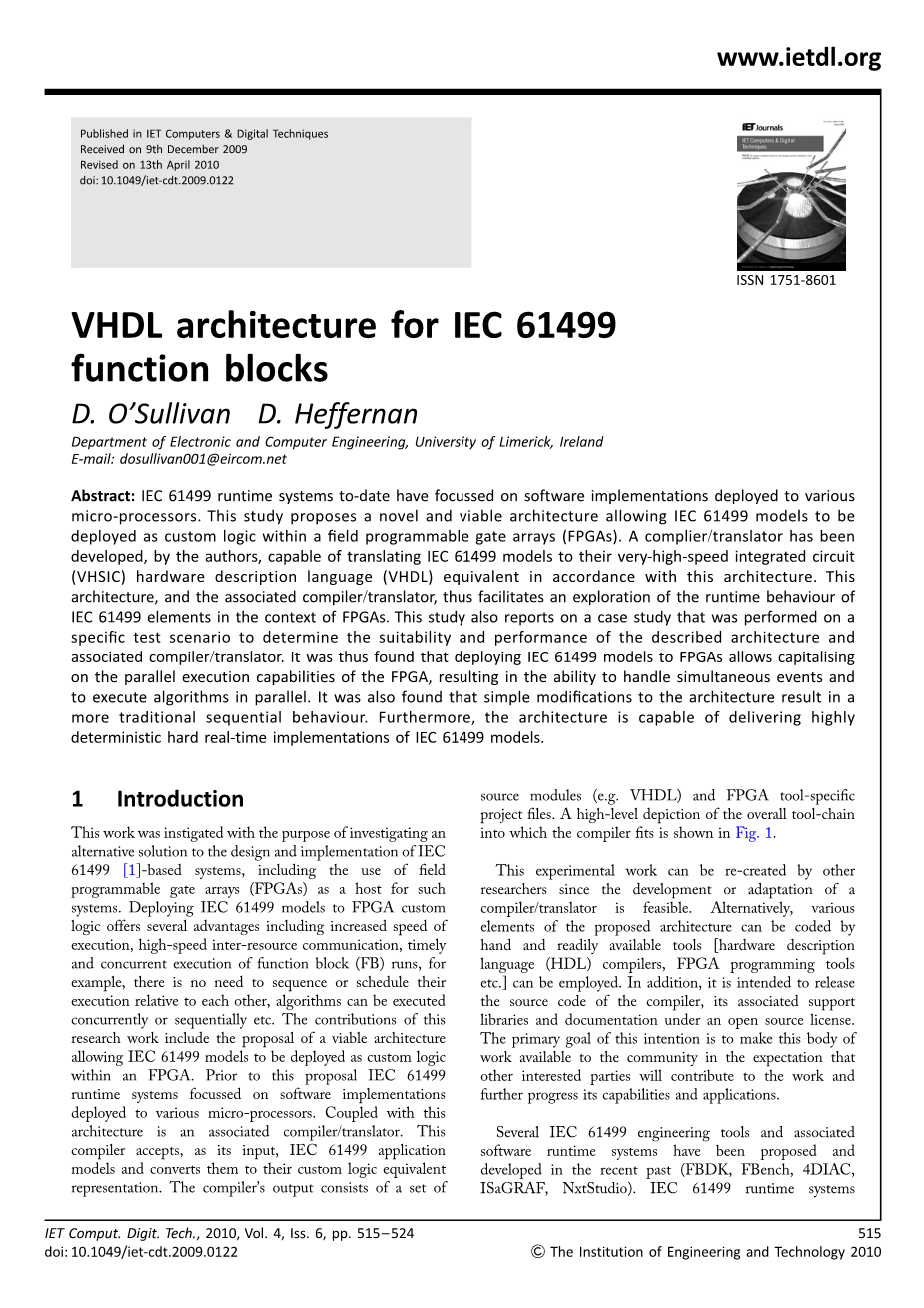

此项研究工作的目的是研究设计和实施基于IEC 61499的系统的替代解决方案,包括使用现场可编程门阵列(FPGA)作为此类系统的主机。定制逻辑提供了几个优点能使IEC 61499模型有效的利用到FPGA,包括增加执行速度,高速资源间通信,功能块(FB)运行的及时和并发执行,例如,无需对其执行进行排序或计划,算法可以同时执行或按顺序执行等。这项研究工作的贡献包括提出一种可行的架构,允许IEC 61499模型作为FPGA内的定制逻辑进行利用。在此提案之前,IEC 61499运行时系统主要被利用到各种微处理器的软件中。加上这个架构是一个关联的编译器/转换器。该编译器接受IEC 61499应用模型作为其输入,并将其转换为其自定义逻辑等效表示。编译器的输出由一组源模块(例如VHDL)和FPGA工具特定的项目文件组成。图1显示了编译器适合的整个工具链的高级描述。

这个实验工作可以由其他研究人员重新创建,因为编译器/译码器的开发或改编是可行的。 或者,可以使用所提出的体系结构的各种元素,并且可以使用易于使用的工具[硬件描述语言(VHDL)编译器,FPGA编程工具等)对其进行编码。 此外,它打算在开源许可证下发布编译器的源代码,其相关的支持库和文档。 这样做的主要目标是使社区能够获得这一工作机会,以期其他感兴趣的各方为工作做出贡献并进一步提高其能力和应用。

过去已经提出并开发了几个IEC 61499工程工具和相关的软件运行时间系统(FBDK,FBench,4DIAC,ISaGRAF,NxtStudio)。迄今为止,IEC 61499运行时系统专注于部署到各种微处理器的软件实现。 一些现有的实现是基于Java的,并且利用了Java本身的各种特性。 在基于C / C 的运行时系统上也有一些工作。 尽管MEDEIA项目已经提到可能包含VHDL,但作者还没有遇到任何专门针对FPGA和HDL的解决方案。本文介绍了一种可行的架构,允许将IEC 61499模型部署为FPGA内的定制逻辑。作者开发了一个编译器/翻译器,它能够根据这种架构将IEC 61499模型转换为等效的VHDL模型。

本文介绍的体系结构有助于IEC 61499应用的建模[即IEC 61499设备和资源的组合,开发复合功能块(CFB)和基本功能块(BFB),编码IEC 61131-3结构化文本(ST)中的BFB算法,集成服务接口功能块(SIFB)]并将这些模型部署到FPGA。 这种体系结构以及相关的编译器/转换器可以帮助您深入了解IEC 61499元素在FPGA环境中的运行时行为。

IEC 61499标准定义了通用架构,并提出了在分布式工业过程测量和控制系统(IPMCS)中使用FB的准则。IPMCS被建模为一个集合,设备通过一个或多个通信网络彼此互连和通信。 由这样的系统执行的功能被建模为应用程序,并且可以驻留在单个设备中或分布在多个设备上。

IEC 61499设备需要与受控过程和更广泛的网络有接口,并且拥有更多资源。该标准支持通过提高功能级别排序的三类设备。IEC 61499资源被认为是一个设备的功能单元,可独立控制它们的操作,并作为应用程序与设备的通信和过程接口之间的桥梁。这种映射是通过SIFB实现的。该资源还负责提供调度功能,其中包括FB之间的通信以及FB算法的及时执行和排序。IEC 61499应用程序构建为一系列互连的BFB,CFB,SIFB和子应用程序。通过将FB实例分配给这些设备的各种资源,可以将这种应用分布到多个设备上。 应用程序的FB之间的功能关系不受其分配的影响。 但是,通信的时间和可靠性将影响分布式应用的时间和可靠性。

FB用于封装一些可重用的功能集,例如PID控制回路。FB的基本形式被称为BFB,它的整体行为被定义为输入事件触发算法和表示块状态改变的事件输出。BFB的执行控制图(ECC)将事件映射到算法。ECC就像一个状态机,因为根据ECC的状态,某些事件的发生会导致某些算法被安排执行。类似地,在算法完成时,ECC将重新提供事件输出信号以表示算法的完成以及在BFB接口处存在关联的数据输出。包含在BFB中的可根据IEC 61131-3编码的算法实际上对用户是隐藏的。 算法接受数据输入来参数化/影响其执行,并将其结果作为数据输出呈现。BFB可能包含私有内部数据,这些私有内部数据会在算法调用之间持续存在,并由算法操纵。循环流化床是由BFB和其他循环流化床收集而成。 它们包含一组有限的FB实例,因此没有ECC,算法或内部数据。SIFB可用于读取/写入设备的输入/输出点,以促进与其他设备/资源的通信,利用设备特定功能等.FB(BFB,CFB和SIFB)被认为是分布的原子单元。子应用程序与CFB类似,只是它们可以分发。

本文的其余部分安排如下。第3节提供了相关工作的概述,第4节描述了提议的体系结构。 第5节描述了一个案例,是使用特定的测试场景执行的,以确定所描述的架构和相关编译器/转换器的适用性和性能。第6节报道了案例研究的结果。该论文在第7节中得出结论。

2 相关工作

Ferrarini和Veber 强调了IEC 61499标准为许多不同地方实现开放的可能性。 他们概述了一系列不同地方的实施可能性并讨论了由此产生的行为。 所有列举的例子都是基于软件的,他们没有分析在FPGA中实现标准的可能性。Hagge和Wagner 对BFB和CFB应用了“基于处理程序的执行模型”(HB-XM)。 他们声称花费很大的努力来实现基于PLC的基于扫描的方式的基于功能块的应用程序,甚至那些说明FB算法的条件执行的实现仍然基本上是基于扫描的。Dubinin和Vyatkin确认并讨论了IEC 61499标准引起的几个执行相关问题,并提出IEC 61499功能块和系统的正式模型。他们担心的是事件调度和数据采样机制,ECC执行和状态转换语义,事件调度的时间顺序以及算法调度和执行之间的关系。 这项工作最终导致他们提出所谓的“顺序假设”是最合适的IEC 61499执行模型。这个假设的核心是“在单个计算容器(IEC 61499术语中的资源)内顺序执行这些块的假设”。他们指出考虑顺序执行功能块的主要原因是现代计算机的顺序特性。Vyatkin等人认识到替代执行模型的可能性,并展示了序贯假设的简单修改如何导致所谓的平行假设。此外,他们承认“并非如此短”的算法,事件分叉场景和多核硬件实现方面的并行模型的#39;更合适#39;和#39;更直观#39;的性质。 在[9]中,顺序假设适用于执行BFB。夏等人研究了并行和管道的原理调度。在他们的工作中,他们表示:“我们的IEC 61499 FB调度方案中使用的并行性不是计算方式,而是计划RDCS中分配的FB的方式。 这意味着物理处理节点(PN),比如现场设备,其中FB驻留在控制回路中的物理处理节点(PN)将不会按顺序工作(只有一个PN可以在一个实例中工作),但会以并行方式工作(所有PN可以同时工作)。 因此,控制周期可以大大减少,以满足周期性要求,并提高分布式控制系统的实时性能。 他们随后[11]展示了如何为联网控制系统提供基于事件驱动的基于FB的DC伺服方法控制系统可以导致比顺序方法更好的控制质量。 但是,他们也指出了有限的网络带宽带来的不良影响。 Yoong等人提出了FB执行的同步语义,并讨论了IEC 61499到Esterel的映射。 随后在Yoong和Roop讨论了自动翻译成Esterel的FB的正式验证。 翻译是使用他们自己的工具进行的,使用Esterel Studio的设计Verier进行了翻译。

关于与FB相关的算法及其向定制逻辑的转换,在可重配硬件中综合某些形式的IEC 61131-3程序方面已经有一些工作; 它主要处理顺序功能图(SFC)和梯形图(LD)的易于转换语言。Ikeshita等人讨论了一个能够将SFC块转换为Verilog HDL的转换程序。 作者成功地将一个SFC程序转换为Verilog等价物,并通过仿真表明,可以使用生成的Verilog模块交付所需的行为。 Miyazawa等人将LD转换为VHDL,同时保留PLC的循环特性。 转换为VHDL是通过为各个阶梯梯级生成等效的布尔表达式并控制其执行顺序来实现的。 相反,Welch和Carletta 针对在FPGA中实现LD应用的问题提出了一种新颖的解决方案。 解决方案的新颖之处围绕在FPGA上实现这种程序的简单和用户友好的概念。 他们的解决方案侧重于模板的配置。该模板由梯级组件组成,梯级组件又由触点块,连接器开关和线圈存储元件组成。接触块和连接器开关都是可配置的模板。这个解决方案可以被看作是应用于LD编程特定领域的底层FPGA构造的更高层次的抽象。

3 自定义逻辑架构

FPGA内部由一组逻辑元件和一个互连结构组成。这些逻辑元件可以在用户看到t时相互连接。这种安排提供了创建实现为一组硬件元素的自定义功能的可能性。这里概述的体系结构显示了如何在FPGA中实现IEC 61499元素。

图2概述了IEC 61499定制逻辑器件的高级视图。 定制逻辑器件支持过程映像接口,通信接口和多种资源。通信交换机用于促进设备内的资源间通信以及设备间通信。 过程映像(输入和输出)连接到各种资源。设备管理器提供了IEC 61499管理模型服务的一个子集。 该设备可以支持多种自定义逻辑资源,确切数量是资源组合大小,通信交换机,设备管理器和目标FPGA大小的函数。 Comms Switch定义取决于资源的资源间和设备间通信要求。 同样,过程映像接口依赖于资源的过程映像需求。 整个定制逻辑设备接口是过程映像接口和通信接口的组合。

图3概述了IEC 61499定制逻辑资源的高级视图。使用一组SIFB将过程接口和通信接口映射到应用程序空间。资源管理器提供IEC 61499管理模型服务的子集。关于提供调度功能,自定义逻辑资源不需要做任何特殊的事情; FB之间的通信可以通过FB实例之间的直接FPGA布线的形式来实现,并且由于资源的FB可以并行运行,所以它们的及时执行得到保证,也就是说,不需要对它们的执行进行排序或安排。

图4概述了IEC 61499定制逻辑BFB的高级视图。BusInHandler和BusOutHandler是负责FB的输入和输出端的事件和数据处理。ECCHandler负责管理FB的状态以响应事件输入的发生,确定应执行哪种算法以及应如何发出事件输出。AlgoHandler负责管理算法的执行和FB的内部数据。FB管理器提供IEC 61499管理模型服务的一个子集。

IEC 61499种类的数据输入应该随着输入事件的到来而被采样和保持。 在检测到输入事件时,与该事件关联的一组数据输入被复制到BusInHandler中的内部寄存器。然后将缓冲的输入(事件和数据)发布到BusInHandler的输出端,使其可用于FB的其余部分。边缘触发采样对应于IEC 61499的概念,即事件瞬时并且无限小。同样在接口的输出侧,数据输出应该随输出事件的发布而更新; BusOutHandler负责此功能。ECCHandler响应于缓冲事件输入的变化和缓冲数据输入的当前状态,管理ECC状态之间的转换,FB拥有内部数据及其生成的输出数据。算法通过将合适的AlgoRun信号传送给AlgoHandler来安排执行。多种算法可以以这种方式同时进行调度。虽然该标准规定应该按顺序执行这些操作,但FPGA提供了调查其并发执行的便利机会。但请注意,该架构很容易支持顺序调用算法。ECCHandler通过AlgoDone信号注意到算法完成。这种信号的到达导致ECCHandler将合适的一组事件输出信号重新发送到BusOutHandler。AlgoHandler负责调度算法,通知ECCHandler它们的完成情况,管理FB的内部数据和输出数据。AlgoRun信号的到来使AlgoHandler激活一种特定的算法。在算法完成后,AlgoHandler必须更新其数据输出并及时通知ECCHandler特定算法的完成情况。

当前支持在IEC 61131-3 ST中编码的算法。有限状态机(FSM)用于控制算法的执行。 在释放算法运行之前,FSM等待AlgoRun信号。然后,FSM在进入其最终状态之前等待算法完成,在该状态下,该算法通过AlgoDone信号发布该算法已完成的事实。FSM可以用来控制简单和复杂的算法。更复杂的算法可以被解构为并行代码的顺序块。FSM提供这些块的顺序执行。

IEC 61499定制逻辑CFB只不过是一组连接在一起的FB,并且在构建时与资源模型类似,并增加了BusInHandler和BusOutHandler。

因为SIFB包装设备特定的功能,所以它们的内部结构通过定义依赖供应商/实施/硬件。 但是,翻译IEC 61499资源与其定制逻辑等价物需要提取其组成SIFB的过程映像和通信要求。 作者对这种情况的解决方案是引入一个实现(.imp)文件。 本文档用于保存SIFB的内部结构,并指定其过程映像和通信要求。 图5显示了这些SIFB实现文件的基本结构。

4 案例分

全文共9408字,剩余内容已隐藏,支付完成后下载完整资料

英语原文共 10 页,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[14481],资料为PDF文档或Word文档,PDF文档可免费转换为Word