英语原文共 12 页,剩余内容已隐藏,支付完成后下载完整资料

两级高效率并行双频带调谐功率放大器

摘要 - 介绍了两级双频带(DB)射频谐波调谐功率放大器(PA)的设计策略和实现。该电路的功率级和驱动级分别设计为在DB-F条件和DB-F反相条件下运行。所提出的功率级的DB谐波控制网络是通过将复合右/左传输线和具有谐波调谐的DB偏置线组合来实现的。开发了一种新型的DB级间匹配网络,将驱动级的最佳基本输出阻抗转换为功率级的最佳基本输入阻抗,并抑制两个频段的三次谐波。在非并联模式(CM)中,两级DB PA的测量输出功率在1.62和2.08 GHz时达到40.2和40 dBm的两个峰值,最大功率附加效率(PAEs)分别为71.5%和73% 。在CM中,最高平均PAE高达62%。据我们所知,文献中首次报道了两阶段并发DB谐波调谐功率放大器的实现。

索引术语 -双频带(DB)高效率功率放大器(PA),谐波调谐,两级。

一,导言

随着现代通信系统(如第三代和第四代系统)的快速发展,许多通信标准已经提出并付诸实施。对于载波聚合的应用,这种多样化的通信标准导致对用于可重构,低成本和高度集成的解决方案的多频带/多标准模式下工作的RF发射机的需求日益增加。众所周知,射频功率放大器(PA)是基站(BS)发射机的RF前端中最具挑战性且昂贵的部件之一,其在高功率附加效率(PAE),高输出功率 ,线性度高,结构紧凑。为了满足多频带/多标准射频发射机的要求,功率放大器必须能够在几个不同的频带内同时工作。

在BS应用中,功耗是最关键的要求,要求使用的PA必须具有高增益和高功率附加效率,无论所需的PA是同时在单个频段还是多个频段中工作。为了增加功率放大器的功率附加效率,人们开始重点研究开关模式或谐波调谐功率放大器,其中F类和逆F类备受关注。在文献[8] - [12]的双频带(DB)中同时进行设计的单级F级功率放大器已经做出努力。而且PAEs虽然没有文献[13] - [15]的单频带F类功率放大器那么高,但它们能在这两个工作频段上工作。 直观上,如果DB无线终端同时在DB中工作,则希望对于两个频带具有类似的PAE。在IEEE IMS2015 [16]我们证明了在1.7和2.14 GHz频率下,设计的DB class-F功率放大器的PAEs几乎相同,测得的PAE分别为78%和77.1%。

两级谐波调谐和开关模式功率放大器的设计在参考文献[17] - [19]中介绍了,工作在一个单一频段。 两级E类PA的总PAE测试为52%[18]。 在文献[19]中使用E类作为功率级和F类作为驱动级的两级功放PAE为50%。 使用F级作为功率级,F级作为驱动级,成功实现了70%的PAE [17]。 其中给出的范例可以得知,如果在F级功率级的输入端进行二次谐波抑制,则可以实现更高的整体PAE。

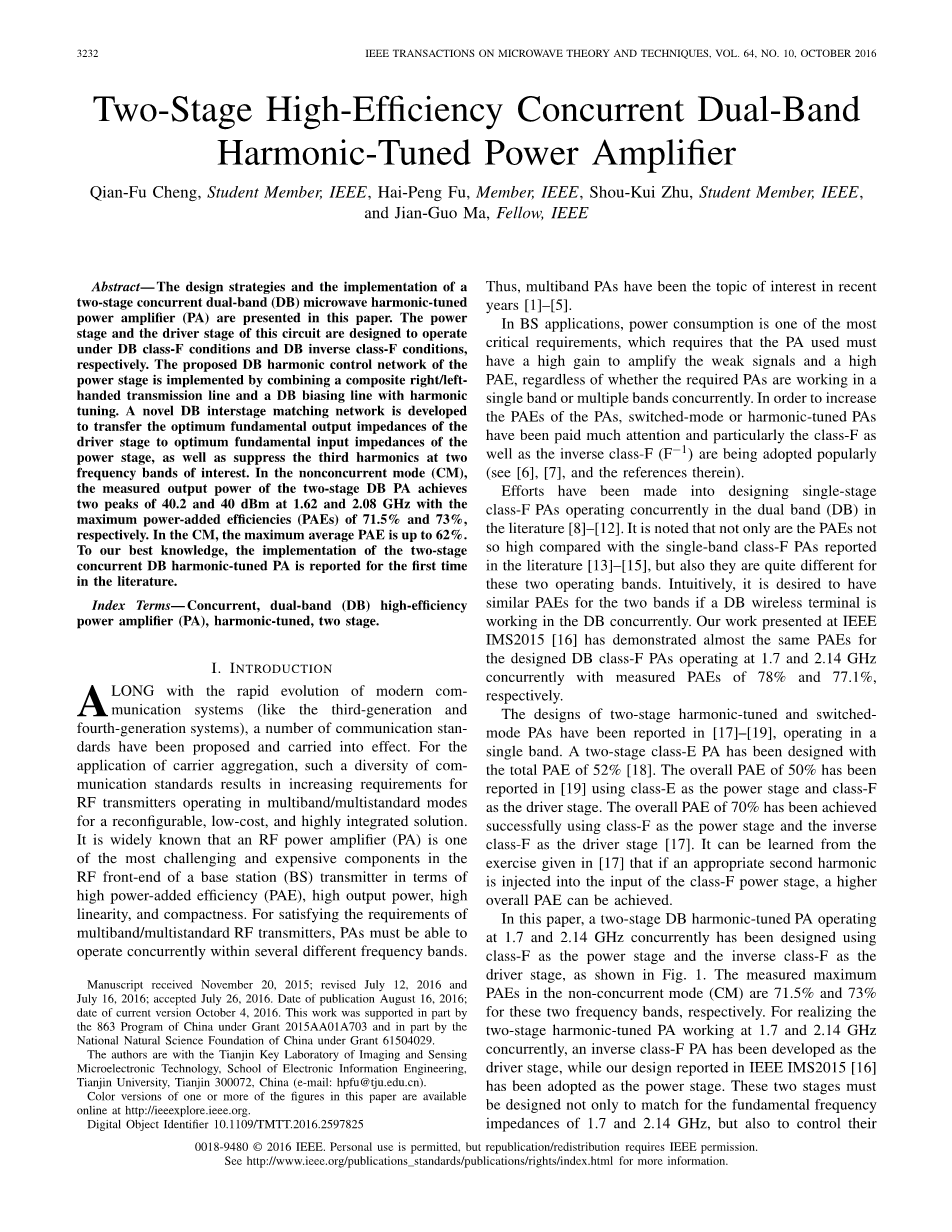

在本文中,设计了1.7和2.14 GHz的两级DB谐波调谐功率放大器以F类作为功率级,逆F类作为驱动级,如图1所示。在非并行模式(CM)下测得的最大PAEs分别为这两个频带的71.5%和73%。为了实现同时工作在1.7和2.14 GHz的两级谐波调谐功率放大器,设计出一种逆F级功率放大器作为驱动级,即在IEEE IMS2015 [16]中报告的设计。这两个阶段的设计不仅要匹配1.7和2.14 GHz的基频阻抗,还要根据F / F-1级阻抗要求来控制其谐波。传统的逆F类设计假设负载是标准的50负载,而驱动器负载则是F类功率放大器。根据文献[17]中提出的设计,F类功率放大器的注入必须是一个基本信号加上适当的谐波,以便设计所需的F类(作为功率级)和逆类F (作为驾驶员阶段)不能简单地遵循标准F / F-1类的传统设计方法。谐波控制是驱动级和功率级匹配的条件。

本文的其余部分安排如下。第二节简要介绍了在IEEE IMS2015中提出的单级DB类F-PA的分析和设计,然后实现了DB-F-PA级。 在第三节中,详细介绍了两级DB谐波调谐功率放大器的设计策略,并讨论了两级谐波调谐功率放大器的测量结果。最后,第四节得出结论。

- 单级双频带F类功率放大器和双频带逆变级功率放大器设计

与传统的两级PA一样,两级DB谐波调谐功率放大器由一个DB功率级和一个DB驱动级组成。功率级主要决定输出功率和PAE,而驱动级影响增益和输入损耗。为了使功放同时在两个频带获得良好的性能,首先需要分别设计单级DB级F-PA和单级DB级-F PA。然后,分别将所提出的两级DB谐波调谐功率放大器的功率级和驱动级分别优化为单级DB class-F PA和DB反相级-F PA。

A.双频段F类功率放大器的简介在IEEE IMS2015

采用IEEE IMS2015报告的单级DB class-F PA作为要设计的两级DB谐波调谐PA的功率级。

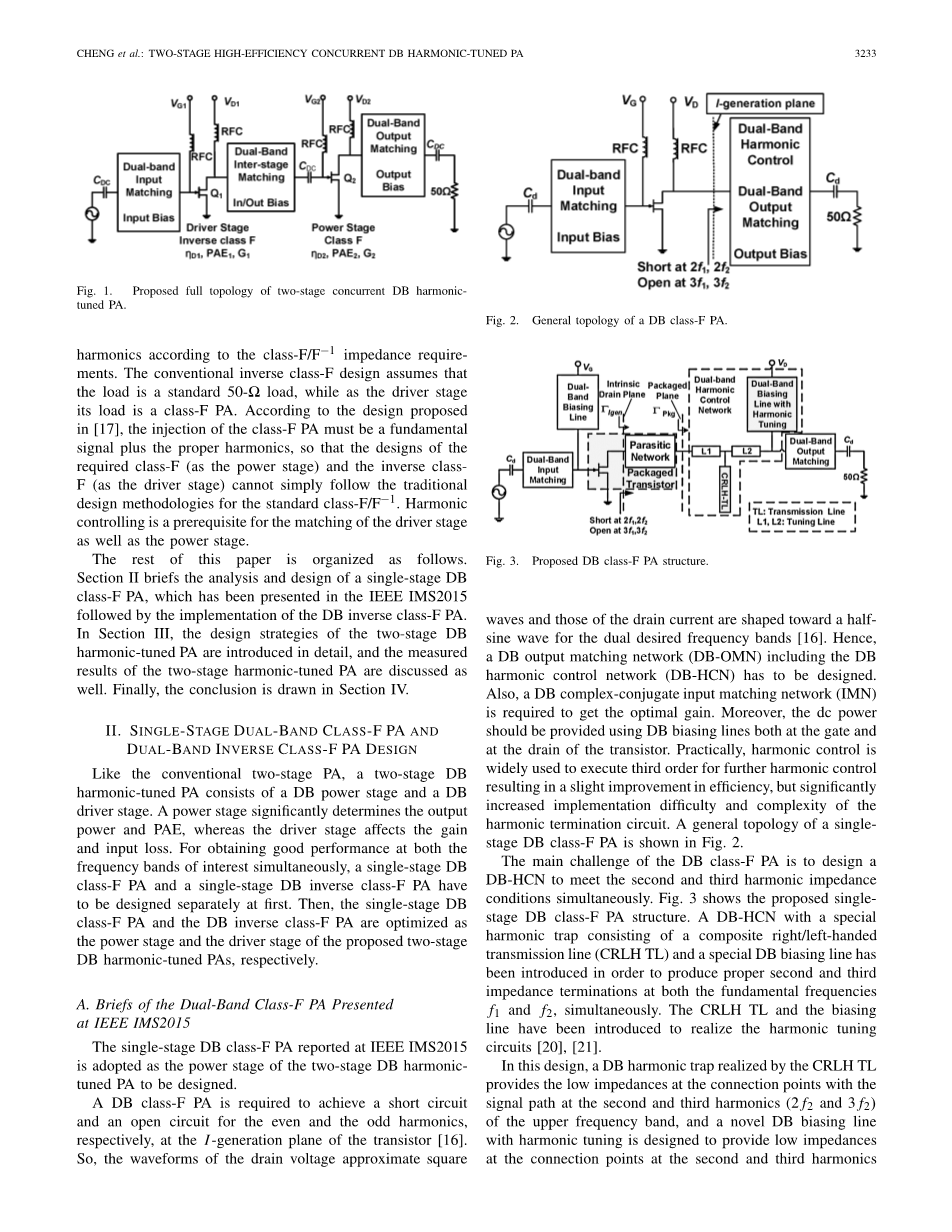

在晶体管层面上,需要DB class-F PA分别实现偶和奇次谐波的短路和开路。 因此,漏极电压近似方波的波形而漏极电流的波形都形成了双频带对应的半正弦波[16]。需要设计具有DB谐波控制网络(DB-HCN)的DB输出匹配网络(DB-OMN)。此外,需要一个DB复数共轭输入匹配网络(IMN)来获得最佳增益。同时应使用晶体管的栅极和漏极处的DB偏置线来提供直流功率。实际上,谐波控制一般控制三阶以上的谐波就只会对效率略有提高,但显着增加了谐波终端电路的实现难度和复杂性。 图2显示了一个单级DB类F-PA的一般拓扑结构。

DB-F PA的设计关键在于设计一个DB-HCN以同时满足二次和三次谐波阻抗条件。 图3表示一般的单级DB class-F PA结构。电路中具有由复合左/右传输线(CRLH TL)和特殊DB偏置线组成的特殊谐波陷阱的DB-HCN,以便在基频f1和f2处产生适当的第二和第三阻抗终端。同时,已引入CRLH TL和偏置线来实现谐波调谐电路[20],[21]。

在这种设计中,由CRLH TL实现的DB谐波陷波在与较高频带的二次和三次谐波(2f2和3f2)处的信号路径的连接点处提供了低阻抗,并且提供了新颖的DB偏置线谐波调谐被设计为在第二和第三谐波的连接点处提供低阻抗。在该设计中,由CRLH TL实现的DB谐波陷波在第二和第三谐波的连接点处提供与信号路径的低阻抗( 2 f2和3 f2),并且设计了一种带有谐波调谐的新型DB偏置线,以便在较低频带的二次和三次谐波(2 f1和3 f1)的连接点处提供低阻抗。然后,在考虑晶体管的寄生元件的同时,仔细调整调整线(L1和L2),可以同时实现两个频段的谐波阻抗条件。因此,实施DB-F PA的主要重点是设计具有谐波调谐的CRLH TL和DB偏置线路的DB谐波陷波器。

理想的CRLH TL通过将理想的右手传输线(RH TL)和理想的左手传输线(LH TL)串联[22]来实现。LH TL显示相位引线的特性,而RH TL执行相位滞后[22]。可以利用这种特性来设计一个DB四分之一波长的传输线结构 [23]。通过将N个单位单元与无限小维度的集总元件串联连接来实现人造TL。相位响应及其导数分别用于设计CRLH TL,如(1)和(2)分别给出[23],

其中L L和L R分别表示LH TL和RH TL的等效集总元件模型的单位单元的电感。同理CL和CR分别表示LH TL和RH TL的单位单元的电容[16]。图4(a)显示了CRLH TL单元单元(N = 1)的集总元件模型。

对于上频带(中心频率f2 = 2.14GHz)的2f2和3f2,使用CRLH TL分别设计-90°和-270°( 90°)的相位以便将高阻抗变为低阻抗。LR 、CR、LL和CL的计算由[23]给出。集总电容器(GQM18)和电感器(LQW18)均来自日本京都的村田制作所。如图4(b)所示,RH部分通过使用(1)和(2)获得的长度的TL来实现。CL和LL的值分别设定为0.5pF和2.4nH。 选择Rogers 5880作为底物,其中h为31mil,εr为2.2。RH TL的最佳长度T1和T2分别为19.1和21.2mm。图4(c)表示谐波调谐器的S21的仿真结果,其中对于较高频带的二次和三次谐波已经实现了短路。

图5(a)表示DB偏置线。在这两个工作频带上,直流电源电压可以被添加到FET的漏极,而不会影响RF信号路径。就f1(1.7 GHz)而言,lambda;1的相应波长而言,使用电长度分别为lambda;1/ 4和lambda;1/ 8的开路短截线T2和T3建立了B点的短路。在A点,电气长度为lambda;1/ 4的TL T1分别使短路在f1处变为开路,在2 f1处变为短路。同时,偏置线的其余部分短路并且对B点处的较低频带没有影响。为了获得具有lambda;2的相应波长的f2处的开路,使用开放的径向短线创建点C处的短路首先。之后,通过调整TL T4的电气长度,实现开路点。此外,由电气长度lambda;1/ 12的开路短截线T5提供3f1的短路。如图5(b)所示,模拟的S21曲线表明低阻抗分别在2 f1和3 f1下实现。

工作频率选择在1.7和2.14 GHz。因此,采用Cree HEMT(CGH40010F)来实验验证所提出的设计理念。它由一个裸露的CGH60015DE GaN芯片和封装(Cree 440 166)构成。封装模型由制造商提供,器件输出寄生模型的近似等效网络如[24]所示。理想的F类阻抗条件是指I代平面,而PA的输出负载网络通常连接到封装参考平面。借助于从器件输出寄生模型近似等效网络中提取的S参数(S P),I代平面处的最佳阻抗ZIgen能够转换到封装参考平面ZPkg,并且可以根据以下公式

然而,固有寄生效应通常是非线性的(与电压有关),这将降低高功率情况下该理论模型的精度。 但制造商为此HEMT提供了非常好的非线性模型,这对设计高效率功率放大器也是有益的。因此,在Keysight Advanced Design System(ADS)的帮助下,使用(3)作为起点,在HENT上进行负载拉动仿真。应该注意的是,这里实现的最佳阻抗是从封装平面获得的,因为晶体管模型包含了封装效应。 此外,使用源拉模拟可以获得最佳的源阻抗。在图6中,阻抗分布情况在史密斯圆图上用于I代平面,包平面,源拉和负载拉模拟。基于这些多谐波阻抗,设计了一个DB IMN(DB-IMN)和一个DB-OMN。

为了最大化DB-F PA的增益,需要DB-IMN。 对于DB-IMN的设计,分布式双端网络用于将50欧姆阻抗转换成两个所需频带处的最佳源阻抗。此外,还增加了一个RC网络以确保稳定性。 为了在两个工作频带向HEMT提供栅极电压,还采用了DB偏置线,其类似于漏极直流偏置线但没有谐波调整功能。

为了使PA在两个频带同时工作,输出匹配网络必须被设计为同时获得每个频带的最佳负载阻抗。在这项工作中,使用DB-IMN的类似拓扑来合成DB-OMN,以在所需频带处最大化PAE。

整个PA是通过将HEMT组合到DB-IMN和DB-OMN中实现的,包括DB-HCN和DB偏置线。为了获得最佳的DB-F PA性能,ADS用于优化整个PA的参数。图7显示了所提出的单级并发DB class-F PA的完整示意图,其在相对介电常数为2.2的Rogers衬底上实现,厚度为31mil。

- 设计单级DB反向F级PA

DB反相级F PA需要二次谐波开路和三次谐波短路,以使漏极电压的波形接近半正弦波,而漏极电流的波形类似于两个方波不同的频段。为了同时满足两个频段的这些谐波阻抗条件,使用与所提出的DB类-F PA类似的DB-HCN拓扑来获得二次和三次谐波阻抗。此处也采用CRLH TL和DB类-F PA中使用的DB偏置线,用于在2f2,3f2,2f1和3f1时提供短路

连接点分别与信号路径。然后,调谐线1和2也用于提供足够的调节自由度,以同时满足在两个频带处的逆F类模式的谐波阻抗条件。相同的GaN HEMT被用作驱动器级的有源器件。由于DB反相级F PA将用作驱动级,因此需要较低的漏极电压。在这种情况下,晶体管在深度AB类模式下偏置,漏极电压Vds = 7 V,漏极电流Ids = 25 mA。 DB class-F-1 PA使用与DB class-F PA相同的基板来实现。建议的DB类-F-1PA在1.7和2.14 GHz设计和仿真。

- 模拟和测量

制造的单级DB class-F PA通过使用HEMT在室温下工作的散热器进行测量和执行。

图8显示了I代平面处晶体管漏极电流和电压的模拟时域波形,而DB class-F PA分别在输出功率为10 W时工作在1.7和2.14 GHz。图8(a)和(b)显示了具有准方波电压和半正弦电流的DB class-F PA的波形,表明在两个工作频带处的明确的class-F行为。

单级DB class-F PA的直流偏置电压为VDS = 28 V和VGS = -2.73 V.直流偏置电流IDS = 50.5 mA。注意,由于10-W HEMT的阈值电压和电子迁移率的差异,所需的栅极偏置电压必须稍微改变以保持模拟和测量电路中相同的直流漏极电流。图9显示了制造的单级DB class-F PA的照片。

在图10中,模拟和测量的输出功率PAE以及非CM中的单级DB class-F PA的增益绘制在两个频带上。如图10所示,DB类-F PA

全文共9596字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[14854],资料为PDF文档或Word文档,PDF文档可免费转换为Word