英语原文共 7 页,剩余内容已隐藏,支付完成后下载完整资料

完整的pi;/ 4-DQPSK调制方案的FPGA实现

摘要

本文讨论了一个集成于数字平台的pi;/ 4-DQPSK的带通调制器,无需外部调制器,混频器,或RF滤波器等。调制和滤波是数字化实现的,从而提供更高的性能和抗噪性。系统采用模块的形式展现,并采用VHDL编码在FPGA上实现。

关键词:FPGA,QPSK,FSK,FIR滤波器,卷积

I.介绍

调制是改变载波的某些特性,以便在给定的带通介质上传输信息的过程。这个过程通常是用基带信号乘以载波然后滤波,可以得到适用于特定带宽的频谱。

在过去的几十年间,由于数字多进制相位调制因其十分简单,已经得到了广泛的研究,特别在与竞争对手正交幅度调制(QAM)相比时,更是如此。pi;/ 4-DQPSK(pi;/ 4差分正交相移键控)是一个四电平调制方案,首先由Baker在1962年提出的,这已被证明在噪声信道中是十分有效的。尽管该项技术已经在美国、日本和欧洲标准上成功的实施,如TDMA蜂窝系统和蓝牙EDR V2.0等,但是这种改进的QPSK继续成为深入研究的重点。

大多数现代数字调器是由模拟和数字电路组成的。如信号映射和滤波是在数字基带频率下完成的。并且最终的调制信号,是由一个外部模拟的射频混频器调制而成的。这种混合信号方案允许在较低频率下使用数字信号处理技术,但仍然会涉及到高频调制。重复算法特别适合于采用DSP技术的高时钟速度处理

许多数字发射机利用重复的算法产生基带信号,然而这些基带信号的产生往往要借助于高速时钟下DSP技术。就目前技术,高达几百KHZ的基带频率可由DSP处理。尽管如此,考虑到一些的调制和滤波技术的性能要求,在FPGA上实施并行数据处理可以满足系统的速度需求。

目前的工作,是在FPGA上完成调制的带通信号的产生。

尽管使用查找表和调制方案的对称性避免了卷积的计算,但是还是要采用FIR滤波以减少符号间干扰(ISI)和频谱扩展。第一部分讨论映射过程,第二部分介绍简化的调制器和滤波器的特性。最后,展示实验结果。

II.信号映射

pi;/ 4-DQPSK调制方案采用两个相同的QPSK星座图,不过一个星座图是另一个旋转pi;/ 4的弧度得到的,pi;/4-DQPSK也是由此得名。偶数符号从一个星座图中选择星座坐标,奇数符号则从另一个星座图中选取。这样做的目的是减少了相位偏移,偏移可以从最高的180°减少为最高的135°,因此降低了频谱的波动。这个星座的转变的另一个好处是信号不通过原点,这也降低了包络波动的范围。因此,与QPSK相比,pi;/4-DQPSK包络变化更小。所以,具有更好的输出频谱特性。从引用[ 6 ]中可以看出该调制方案的进一步细节和优点。

星座图和可能的符号间转换如图1所示。

图1 pi;/ 4-DQPSK 信号星座图

为了允许差分检测,信息的编码是根据符号的跳变,而不是根据符号本身,即进行的是差分编码。

对于初始符号,有四种可能的转换,因为调制方案规定了一个符号可以跳变到另一组星座图中的任何一个符号。相位表现为以两路数据的不同的组合方式输入,使得偶数和奇数星座图的符号交替发送。因为有四个不同的可能性,每次传输可以传输两位信息(一个a dibit)叫做。输入数据的每一个组合都对应于一个相应的相移。

符号转换的一个例子如图2所示。要发送的下一个符号取决于输入数据和最后发送的符号。

图2 相移示例

考虑到,例如,在图2中对应于pi;/ 4相位的初始符号1,如果输入的数据是= 00,对应的相移为-3pi;/ 4,从而跳转到符号6。同样的分析,还可以生成的符号有0, 2和4。注意,初始符号是一个奇数,所有四个可能的下一个符号都是偶数,这一点在调制方案曾提到过。

这种类型的差分方案与有限状态机(FSM)图的一部分的相似之处可以通过检查图2找到。星座上的符号可以与Moore型状态机上的八个状态S相对应,根据每种输入组合可以得到4个可能的转换

为了产生一个调制信号,每个状态被移动到一个缓冲区,它由一个具有独立写和读地址的循环存储器组成。每次转换后,内存写入地址都会增加,并且存储的数据代表调制器的输入。图3显示了该方案的基本框图。

图3 提出的结构:信号映射器、寄存器和调制器

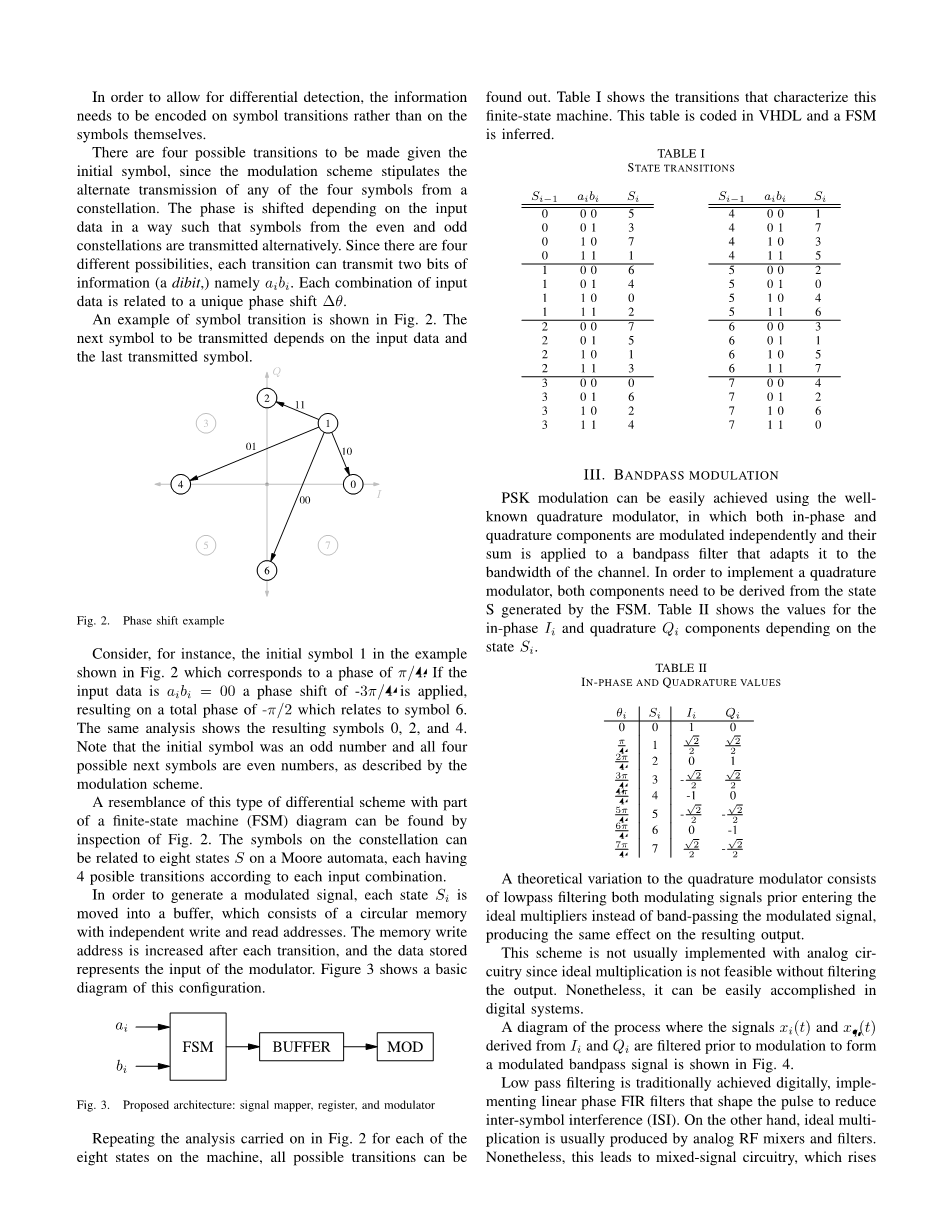

逐个分析图2中的每一个初始状态,可以得出所有转换的可能。采用VHDL硬件描述语言编写的FSM,得到有限状态机所有的转换可能,表1所示。

表1 状态转换

III.带通调制

PSK调制可以使用我们熟知的正交调制器很容易的实现,其中同相和正交分量进行独立调制后相加得到最终的调制信号,经过带通滤波器后可以很好的适用带通的信道。为了实现正交调制器,需要从FSM生成的状态导出同相和正交的这两个分量。表2显示了Ii和Qi组成的值,取决于状态Si。

表2 同相和正交分量值

正交调制器的一个转变是:在进入理想乘法器之前对两个调制信号进行低通滤波,而不是对调制信号进行带通滤波,但是这两种方式产生的效果相同。

该方案通常不采用模拟电路实施,是因为理想的乘法是做不到无滤波输出的。然而它可以很容易采用数字系统实现。

整个过程的展示如图4所示,信号xi(t)和xq(t)来自Ii和Qi,在进行调制之前经过LPF滤波器,然后进行调制。

数字滤波器是对传统低通滤波器进行数字化实现,使用线性相位FIR滤波器进行脉冲成型以便实现去除符号间干扰(ISI)。另一方面,理想的多应用通常是通过模拟射频混频器和滤波器产生的。然而,这引入了混合电路,增加系统的成本和复杂性。此外,在许多应用中,载波频率不超过兆赫的屏障,但是可以在数字平台产生的信号的调制信号,避免了使用任何模拟子系统。

图4 正交调制器

FIR滤波器可以很容易地使用窗口设计衍生出来的,将一个特定的窗函数加在无限脉冲响应(IIR)滤波器上实现的[ 7 ]。平方根升余弦滤波器(SRRC)用于脉冲整形数字调制,可以很好的减少ISI,匹配滤波效果较好,因为这样两滤波器响应的结合是升余弦滤波器的优化得到的[8]。

考虑到滚降系数为0.35,根据以往实验结果[5]。方形窗口的选择是为了保证无ISI且性能不受影响,这样会截断脉冲的响应。当在t =plusmn;2T时候截断,会出现轻微的频谱发散。

举例来说,如图5所示,16个滤波器抽头在原点处用偏移量进行采样,这简化了硬件实现。变量k表示存储在存储器中的值的地址。但是考虑到滤波脉冲的对称性,因此k只能从0到7。

图5 采样FIR滤波器

考虑两位序列dibit:ab={ 11 11 10 }和初始状态S = 7。相应的相位变化theta;= { pi;/ 4 pi;/ 4 -pi;/ 4}。因此,FSM将以F ={7,0,1,0}的状态加载缓冲区。这些值稍后将会被用来产生调制信号。

从表2中获得的同相分量的相序,可以表示为图6中的时间函数。

该序列与脉冲整形滤波器h(k)的卷积,可以被认为是以T的倍数为中心并由系数Ii加权的脉冲h(t)的采样和。

因为:

图6 Ii例子

此外,由于采样滤波器h(k)在信号发送两个周期(频率v = 1 / T)之后被截断,所以仅需要最后四个状态就能生成完整的滤波信号。因此,循环存储器只需要四个位置。

需要获得同相分量滤波结果的过程如图7所示。虚线表示采样点,变量A、B、C和D是整形脉冲的每个转换版本的索引或指针。这些信号的总和可以计算出分量xi,而分量xi原本是期望从卷积特性中得到的。

图7 xi的产生

因此,获得滤波后的信号就如同整形脉冲的加权和转换一样简单,可以从查找表(LUT)中获得。该滤波器的实现是在下一节中详细讨论。

下一步完成由信号xi和xq与两路正交信号相乘的调制器部分。

如果调整载波与信号频率(nu;= 1/ T)之间的关系,使得每个信号都采用整数个载波周期,同相分量的表达可写为

其中,hI(t)是调制脉冲,因为

当选择载波与信号频率比为5时,该脉冲如图8所示。 由于两个偶函数的乘积产生另一个偶函数,仍然满足对称性。

图8 调制同相滤波脉冲

以同样的方式,调制分量xq(t)可以得到采样脉冲。增加脉冲的反射时候需要特别注意,因为它现在是一个奇方程。

由于两个调制脉冲的频谱特性都不同于原始信号,因此采样频率需要大幅增加。以最大频率的两倍进行采样是不够的,因为它引入了高相位失真,这在相位调制系统中是不希望的。另一方面,过采样会导致更多的滤波器抽头,因此会导致更高的计算和内存成本。因此,必须采用折衷条件。

最后,可以适用于线性放大器并且可以传输的调制信号可以用一个求和的式子表示出来:

实施

已经表明,根据pi;/ 4-dqpsk调制方案,一个调制带通信号的产生可以将整个过程用卷积,滤波器,周期信号的性质分为几个部分。

本部分的目的是:设计把数据加载到循环缓冲区的电路,以及输出完全调制和滤波信号的电路,避免各种卷积和乘法运算,从而减少计算的要求。

卷积传统上是串行操作,通常是用存储在累加器中的乘法序列实现的。另外,一个抽头延迟线的FIR滤波器可以在并行架构的FPGA中实现,如图9所示。

这种体系结构是卷积算法的一种简单实现,它利用了大量的乘法器和延迟。

虽然在文献中可以找到不同的卷积的架构,但是它们都可以在设计时进行彻底优化。如图6所示,输入信号总是一个deltas序列,这会产生大量的空乘法运算,使得抽头延迟线滤波器甚至任何采用这样体系结构设计都是一个糟糕的选择。

图9 线性滤波器的抽头延迟

为了充分利用已知的调制方案,提出图10所示的系统。在这种配置的调制信号是由存储在缓冲区中的四个状态加相形成了一个独特的输出。在时钟的第一个周期的前半部分分析存储器,然后下半部分,清除累加器。因为各自属性不同,偶数(e)和奇数(o)符号由独立映射块(map-)处理。

图10 提出的调制器架构

偶数符号的同相和正交分量的振幅总是 1、-1或0这个几个值,但它们的平方不能同时为1。因此,不需要计算一个给定的符号信号的同相分量,因此,如果正交分量的值为plusmn;1,则不需要计算给定符号的信号的滤波同相分量,反之亦然。因此,在顶层的多路复用器之后,只有一个映射块是必需的。

因为奇数符号的同相和正交都是与相关,所以底层的复用器,一个反馈给同相映射块,另一个反馈给正交映射块。但是各自都不受限于另一方。

映射块向加法器输送存储在缓冲器中的部分调制信号。为此,调制脉冲的右侧部分将被采样,并存储在查找表中,并且根据缓冲器的读取和写入地址的相对位置来推断地址。最后,信号的符号根据星座中符号的位置而改变。

三个模块的工作类似,每一个都有自己特定的属性。图11显示了这些基本框图模块。

从图7分析的卷积性质可以推导出,在T和2T之间显示的区域是感兴趣的,因为它是唯一一个四个脉冲全都是非零值的区域。

图11 信号映射和寄存器

用于访问LUT的地址可以从唯一的全局计数器中获得。 例如,如果计数器与地址B相关联,则可以使用表达式计算地址A,C和D.

A = B 4 C = 3 – B D = 7 – B

从二进制数的基本属性可以看出,这些表达式更普遍地表示成:

D=

其中每个bi是二进制表示,B = 0 到2M-1。

因此,四个地址中的任何一个都可以通过全局计数器上的基本逻辑操作获得。 使用哪些地址取决于循环缓冲区的读取和写入地址之间的关系。写地址(W)是系统中可用的变量,读地址取决于CLK。 CLK = 0时读取第一个和第二个元素,CLK = 1时读取第三个和第四个元素。

表3 偶数和奇数符号地址

由图7中检验,可以得出对应的奇偶符号AE和AO的地址,如表3所示。

偶数符号映射块

如前所述,奇数符号可以只有一个分量,可以是同相或正交,但不能同具有时同相或正交分量。因此,没有必要用两个独立的查找表,因为他们不会同时访问。相反,上半部分是同相脉冲HI,下半部分是HQ来创建一张大表。用于访问查找表的地址是来源于表三的一个级联的AE。当内存中的符号是0或者4(Ii = plusmn;1),H是0,当内存中的符号是2或者6(Qi = plusmn;1),H是1。

存储在查找表中的数据对应的正脉冲HI和HQ的右侧。因此,需要根据星座中的符号位置和脉冲的对称性来改变产生的值的符号。

HI是一个偶函数,符号只取决于状态S

全文共6608字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[16970],资料为PDF文档或Word文档,PDF文档可免费转换为Word