英语原文共 6 页,剩余内容已隐藏,支付完成后下载完整资料

适用于低成本低功耗应用的LTPS薄膜晶体管

Soo Youn Kim,Selin Baytok和Kaushik Roy

普渡大学,西拉法叶,美国

电子邮件:sookim@purdue.edu

摘要:低温多晶硅薄膜晶体管(LTPS TFT)已经成为诸如低成本传感器网络等应用的有前景的技术。 在本文中,我们提出了一种基于硅体尺寸()和掩埋氧化层厚度()的LTPS TFT器件优化方法。 所提出的方法适用于数字和模拟电路。 结果表明,与传统器件相比,使用所提出的器件,我们可以实现三级环形振荡器(RO)的振荡频率的133倍提高和运算放大器(OPAMP)增益( = 10nm和 = 10nm)的31%改善结构。 我们认为,为了实现低功耗,高性能,低成本的LTPTS TFT数字和模拟/射频电路,必须正确优化TFT器件几何参数。

关键词:

掩埋氧化物(BOX),埋氧化物感应势垒降低(BIBL),漏感应势垒降低(DIBL),薄膜晶体管(TFT)

- 介绍

对于在柔性或玻璃基板上需要低成本传感器节点,无线电和数字电子设备的应用,低功耗电路的需求日益增长[1]。这些应用通常由电池供电,并且可能无法随时更换电池。而且,这样的系统由数字和模拟/ RF电路块组成。请注意,由于与晶体硅(c-Si)电路制造相关的高成本或需要柔性衬底,因此标准CMOS可能不适用于此类应用。因此,已开始认真开发用于此类应用的低成本CMOS电压兼容器件。低温多晶硅薄膜晶体管(LTPS TFT)(图1)已被提议作为这种电路的合适候选者,主要由于低制造成本。然而,由于当今大型器件的高电源需求(VDDgt; 10V,因为多晶硅(poly-Si)可能在沟道中有大量的晶粒,所以功耗仍然是此类器件的瓶颈,导致比c-Si低得多的迁移率)。因此,VDD缩放对于提高此类器件的功耗至关重要。但是,电路性能指标(如延迟,频率响应等)会在较低的VDD下降级。因此,VDD缩放必须与缩放信道长度一起使用,以提高电路性能。请注意,通道长度缩放还可以改善通道中的晶界数量(GB),从而提高移动性。然而,短沟道器件的门极可控性较差,导致IOFF较高,输出电阻较低(击穿)。这些影响有减少较短信道长度的好处。因此,需要研究和改进器件静电以实现卓越的电路性能。在以前的工作[2]中,作者指出,LTPS-TFT硅基体厚度()的缩放可以提高数字操作的亚阈值区域的性能。然而,[2](6nm)中使用的超薄(低于10nm)会由于表面粗糙度散射增加而导致严重的迁移率下降[3]。而且,对于一般在饱和区工作的模拟电路来说,采用这样的概念是困难的。因此,有必要探索替代器件结构来提高数字和模拟电路的性能。

在本文中,我们提出了适用于数字和模拟应用的VDD缩放和改进的器件和电路性能的器件结构。请注意,为了设计低功耗数字电路,器件需要表现出高ION / IOFF比。另一方面,对于模拟电路而言,重要的器件指标是固有增益(AV0),它取决于跨导(gm)和击穿。我们提出的方法可以提供改进的数字和模拟性能指标(ION / IOFF比率和AV0)。总之,我们的设备设计/优化方法由三个步骤组成:

bull;LTPS TFT中二维效应的物理建模

bull;基于上述物理模型对设备进行了优化,以改善数字和模拟指标

bull;用于电路仿真的紧凑型模型开发。

本文的其余部分安排如下。在第2节中,我们详细解释了器件设计,建模和优化方法。此外,根据ION / IOFF比率,漏极感应势垒降低(DBL),gm和击穿等器件指标,优化器件与标准LTPS TFT器件进行比较。基于第2节的优化设计,我们设计了两个基准电路:三级环形振荡器(RO)和运算放大器(OPAMP),结果在第3节中讨论。此外,晶体管阈值电压(VT)在LTPS TFT中的GB位置在第3节中进行了分析。最后,我们在第4节中总结了本文。

2.设备结构和建模

2.1设备结构

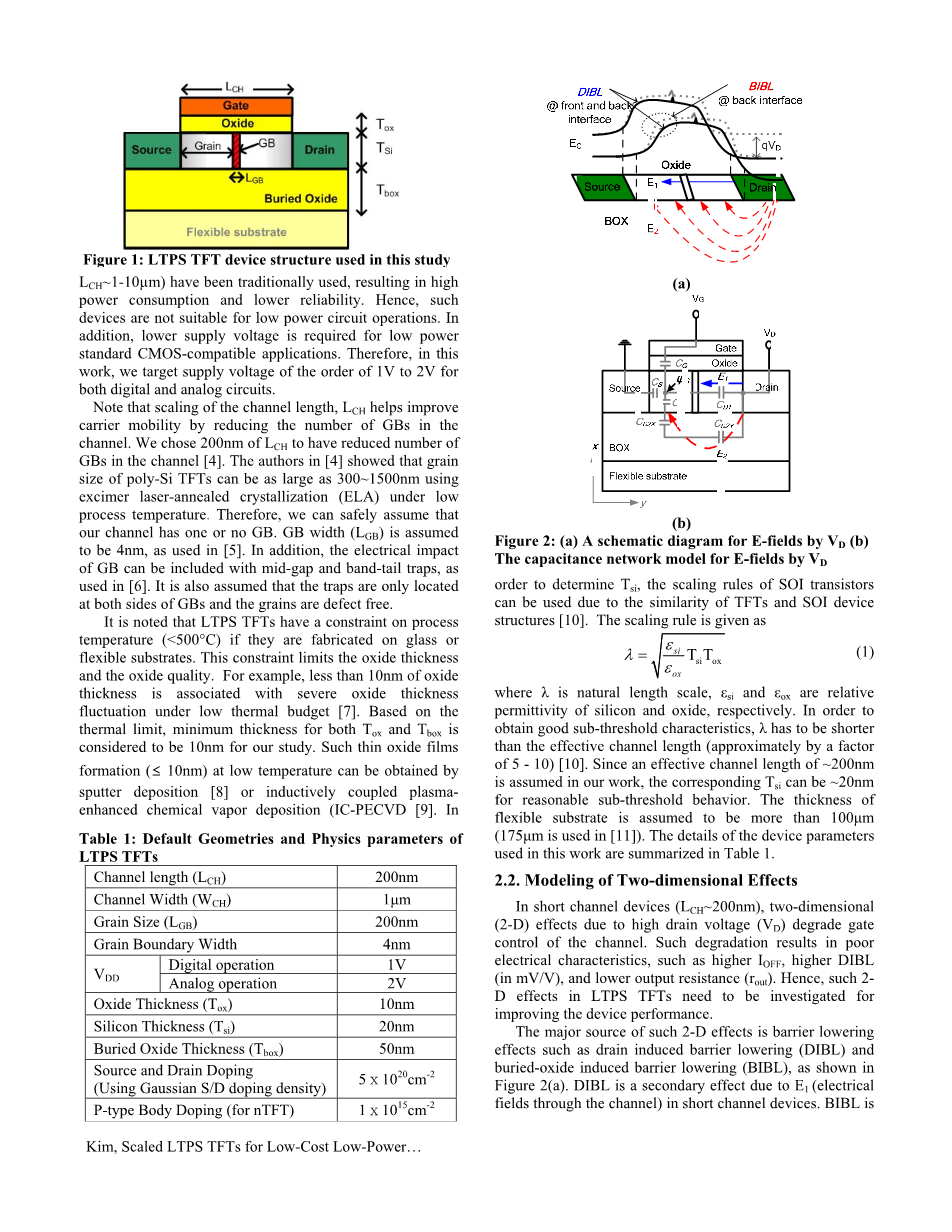

LTPS TFT具有如图1所示的SOI(绝缘体上硅)结构。然而,沟道材料是具有GB的多晶Si。 GB降低载流子迁移率,导致器件特性差,包括不同器件中阈值电压(VT)的变化,逐渐亚阈值斜率和低ION / IOFF。 为了满足具有如此差的电特性,高电源电压(VDDgt; 10V)和大型器件几何结构的电路性能(通道长度:第12届国际质量电子设计研讨会

图1:本研究中使用的LTPS TFT器件结构

LCH〜1-10mu;m)传统上使用,导致高功耗和低可靠性。 因此,这样的设备不适合低功率电路操作。 另外,低功耗标准CMOS兼容应用需要较低的电源电压。 因此,在这项工作中,我们将数字和模拟电路的电源电压定为1V至2V。请注意,缩放信道长度LCH有助于通过减少信道中的GB数量来提高载波移动性。我们选择200nm的LCH来减少通道中的GB数量[4]。文献[4]的作者表明,在低的工艺温度下,使用准分子激光退火结晶(ELA),多晶硅TFT的晶粒尺寸可以高达300〜1500nm。因此,我们可以放心地假设我们的频道有一个或没有GB。 GB宽度(LGB)假定为4nm,如[5]中所用。此外,如[6]中所用,GB的电气影响可以包括在中间隙和带尾陷阱中。还假定陷阱仅位于GB的两侧,并且谷粒没有缺陷。

表1:LTPS TFT的默认几何和物理参数

|

Channel length (LCH) |

200nm |

|

|

Channel Width (WCH) |

1micro;m |

|

|

Grain Size (LGB) |

200nm |

|

|

Grain Boundary Width |

4nm |

|

|

VDD |

Digital operation |

1V |

|

Analog operation |

2V |

|

|

Oxide Thickness (Tox) |

10nm |

|

|

Silicon Thickness (Tsi) |

20nm |

|

|

Buried Oxide Thickness (Tbox) |

50nm |

|

|

Source and Drain Doping (Using Gaussian S/D doping density) |

5ค1020cm-2 |

|

|

P-type Body Doping (for nTFT) |

1ค1015cm-2 |

|

(a)

(b)

图2:(a)VD的电场示意图(b)VD的电场电容网络模型

(b) The capacitance network model for E-fields by VD

值得注意的是,如果LTPS薄膜晶体管制造在玻璃或柔性衬底上,它们对工艺温度(lt;500℃)具有约束。这个约束限制了氧化物的厚度和氧化物质量。例如,在低热预算下,小于10nm的氧化层厚度与严重的氧化层厚度波动有关[7]。基于热极限,和的最小厚度在我们的研究中被认为是10nm。通过溅射沉积[8]或电感耦合等离子体增强化学气相沉积(IC-PECVD [9])可以获得低温下的这种薄氧化膜形成(〜10nm)。为了确定,SOI的缩放规则由于TFT和SOI器件结构的相似性,可以使用晶体管[10]。缩放规则如下

其中lambda;是自然长度尺度,和分别是硅和氧化物的相对介电常数。 为了获得良好的亚阈值特性,lambda;必须比有效信道长度短(约为5 - 10倍)[10]。 由于在我们的工作中假设有效通道长度为〜200nm,相应的可以为〜20nm,以达到合理的亚阈值行为。 假定柔性衬底的厚度大于100mu;m([11]中使用175mu;m)。 表1总结了本工作中使用的器件参数的详细信息。

2.2二维效果的建模

在短沟道器件(LCH〜200nm)中,由高漏极电压(VD)引起的二维(2-D)效应降低了沟道的栅极控制。这种退化导致较差的电气特性,例如较高的IOFF,较高的DIBL(mV / V)和较低的输出电阻(击穿)。因此,需要研究LTPS TFT中的这种2-D效应以改善器件性能。

如图2(a)所示,这种2-D效应的主要来源是屏障降低效应,如漏极诱导屏障降低(DIBL)和掩埋氧化物诱导屏障降低(BIBL)。由于短信道设备中的E1(通过电信道的电场),DIBL是次要效应。 BIBL是E2的另一个屏障降低效应(穿透BOX的电场)。 BIBL是带有BOX的器件的固有特性,它进一步降低了背面接口附近通道的门控可控性,如图2(a)所示,

为了定量分析LTPS TFT中的电场E1和E2,使用电容网络模型[12]。图2(b)显示了相应的电容

电场。 CD1和集总电容CD2X和CD2Y分别代表对应于E1和E2的静电耦合。 CG是栅极电容(〜CoxWCHLCH),CI是反转层电容,CD1是沟道 - 漏极电容,CD2是表示边缘电场的CD2X和CD2Y的串联电容。前面描述的电容表达式由Eq提供的。

CI,CD2X和CD2Y串联连接。 当小于LCH时,CD2Y总是小于CD2X和CI。 因此,等效串联电容可以近似为CD2Y。 因此,当施加VG和VD时,由于2-D效应,表面电位; s由VG和VD控制,如方程(3)。

哪里

因此,为了获得更高的栅极可控性=,CG应该大于CD1 CD2Y,如方程(4)。

因此,,和的降低可以有效降低2-D效应,从而提高设备性能。

为了验证这种电容网络模型,Taurus [13]是一种商用的二维漂移扩散求解器。 由于的缩放因工艺温度而受限制,因此我们通过和的缩放来调查器件性能。 对于低功耗数字操作,要优化的关键器件指标是DIBL(mV / V)和

ION / IOFF比率。 而且,2-D效应也会影响模拟电路,因此有必要研究路由。 在下一节中,我们将详细讨论模拟和数字性能指标的分析和优化,以实现基于LTPS TFT的低功耗设计。

3.技术/电路协同优化

为了优化器件,我们通过比例尺和提供了二维器件模拟[13]结果,并分析了DIBL,ION / IOFF比率和击穿。在优化器件的基础上,设计并分析了两个典型电路,一个三级RO和一个OPAMP。

图3:设备仿真结果显示(a)默认缩放条件的ID-VG曲线中的DIBL(mV / V)(= 50nm, = 20nm),(b)缩放( = 50nm, = 10nm)和(c)缩放(= 10nm,= 20nm)

图4:和对(a)DIBL,(b)ION / IOFF比例和(c)在iso-IOFF条件下缩放和的ID-VG曲线的影响

3.1数字操作(VDD = 1V)

为了评估数字特性,我们研究了缩放和的DIBL(单位为mV / V)和ION / IOFF比率。当施加高VD时,势垒高度降低,导致VT降低。在ID = 10-8A /mu;m时,分别在VD = 50mV(VT,lin)和VD = 1V(VT,sat)下计算VT。结果表明,如图3(a)所示,DIBL在默认比例条件下( = 20nm, = 50nm)为232mV / V。图3(b)和3(c)显示DIBL可通过(10nm)缩放降至116mV / V,并且通过缩放(10nm)降至171mV / V。结果表明,当和同时缩小( = 10nm, = 10nm)时,可以实现最小的DIBL,从而产生64mV / V的DIBL(图4(a))。通过抑制2-D效应改进DIBL可以改善门极可控性并降低IOFF。结果表明,与图4(b)所示的默认缩放条件相比,使用薄缩放导致ION / IOFF比率提高了142倍。值得注意的是,随着的缩放,栅极电容几乎保持不变[2]。对于此分析中使用的器件,金属栅极功函数是变化的以获得iso-IOFF条件。在iso-IOFF下,由于ION较高,可以获得改进的亚阈值操作,如图4(c)所示。采用默认缩放条件( = 20nm, = 50nm),三阶段RO的延迟(ı)计算为72.8nsec。缩放和的线索

以改善ı(0.55nsec)。表2列出了数字操作器件特性的汇总结果

另外,与FD-SOI不同,LTPS TFT的浮动衬底不会为缩放提供

全文共11319字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[11322],资料为PDF文档或Word文档,PDF文档可免费转换为Word