英语原文共 4 页,剩余内容已隐藏,支付完成后下载完整资料

附录A 译文

W/Ta2O5/W MIM电容器与底部电极厚度的漏电流特性变化

摘要:在这篇论文中,我们将说明泄漏电流特性可以是底部电极的函数。底部W电极厚度变化对W/Ta2O5/WMIM电容器漏电流特性的影响。其主要通过两种机制,第一种机制是通过Ta2O5化学气相沉积过程可以影响W底电极厚度。实验中观察到通过CVD法沉积的Ta2O5薄膜在不同的底电沉积条件下具有明显的差异。第二种机制是底部W电极的表面粗糙度会随厚度增加而增加,导致较小的有效肖特基势垒高度。更小的有效肖特基势垒高度会导致较大的泄漏电流。

关键词:Ta2O5,表面粗糙度,曲面光顺,有效肖特基势垒高度。

- 绪论

金属-绝缘体-金属(MIM)电容器应用于模拟/混合信号CMOS集成电路中[1,2]。通过更先进的技术,高介电材料已被用来取代传统的介电材料,如SiO2或Si3N4〔3—5〕。如果漏电流较低,这有可能是使用了更薄的高介质膜,导致更大的电容密度。此外,MIM结构还被研究对RRAM(电阻随机存取存储器)应用(6—8)。对于以上讨论的应用,泄漏电流与电压(I -V)特性是很重要的。然而,底层物理学对MIM薄膜电容器包含高电介质的IV特性仍不清楚。这样就迫切地需要了解更深层次MIM电容器的漏电流特性。

在本文中,我们将注意力集中在通过化学气相沉积(CVD)的Ta2O5作为MIM电容器的介电材料上,因为它是一种很好的能证明高介电常数技术的材料〔9〕。Ta2O5的相对介电常数为20~25,与SiO2的4相比(10—12)。基于Ta2O5或其它高介电常数材料的MIM电容器都趋向于呈现不对称的电流-电压(I—V)。即使顶部和底部电极都是由明显对称结构的同种金属制成。另外,当底部金属电极的厚度变化时,它的I -V特性也随之发生改变。

2 实验

在我们的实验中,氧化钽(Ta2O5)通过CVD沉积在裸片(100)Si晶片或W涂层(100)Si晶片上,类似于麦金利和桑德勒(9)的实验;钨涂层是通过溅射完成的。氧化钽用Ta(OC2H5)5的化学式作为前驱体,氧(O2)用作氧化剂。然后通过金属荫罩形成顶部金属接触件,钨(W)再次溅射到Ta2O5薄膜的顶部。这个过程中可能存在溅射过程中的“等离子体损伤”。在W溅射后400℃,在氮气中进行退火(PMA)。然后用安捷伦公司I-V测量的B1500 A半导体器件分析仪对Ta2O5电容器电特性进行了表征。

AFM用来测量溅射到硅片上的钨的表面粗糙度。同样,AFM可以用来测量 通过CVD后的Ta2O5薄膜的顶部的粗糙度。通过透射电子显微镜(XTEM)观察横截面来研究界面粗糙度。通过聚焦离子束(FIB)技术来制备XTEM样品。为了保护顶部表面的Ta2O5薄膜,在FIB之前,我们在Ta2O5薄膜的顶部沉积了Al膜。之所以用Al是因为透射电子性能中的氧化物或钨显微镜检查它比钽对电子更透明。如果使用钨作为顶部保护层,钽氧化物尖峰可能很难被探测到。FIB后的Al/Ta2O5/W/Si结构的横截面通过透射电子显微镜来研究。

3 结果和讨论

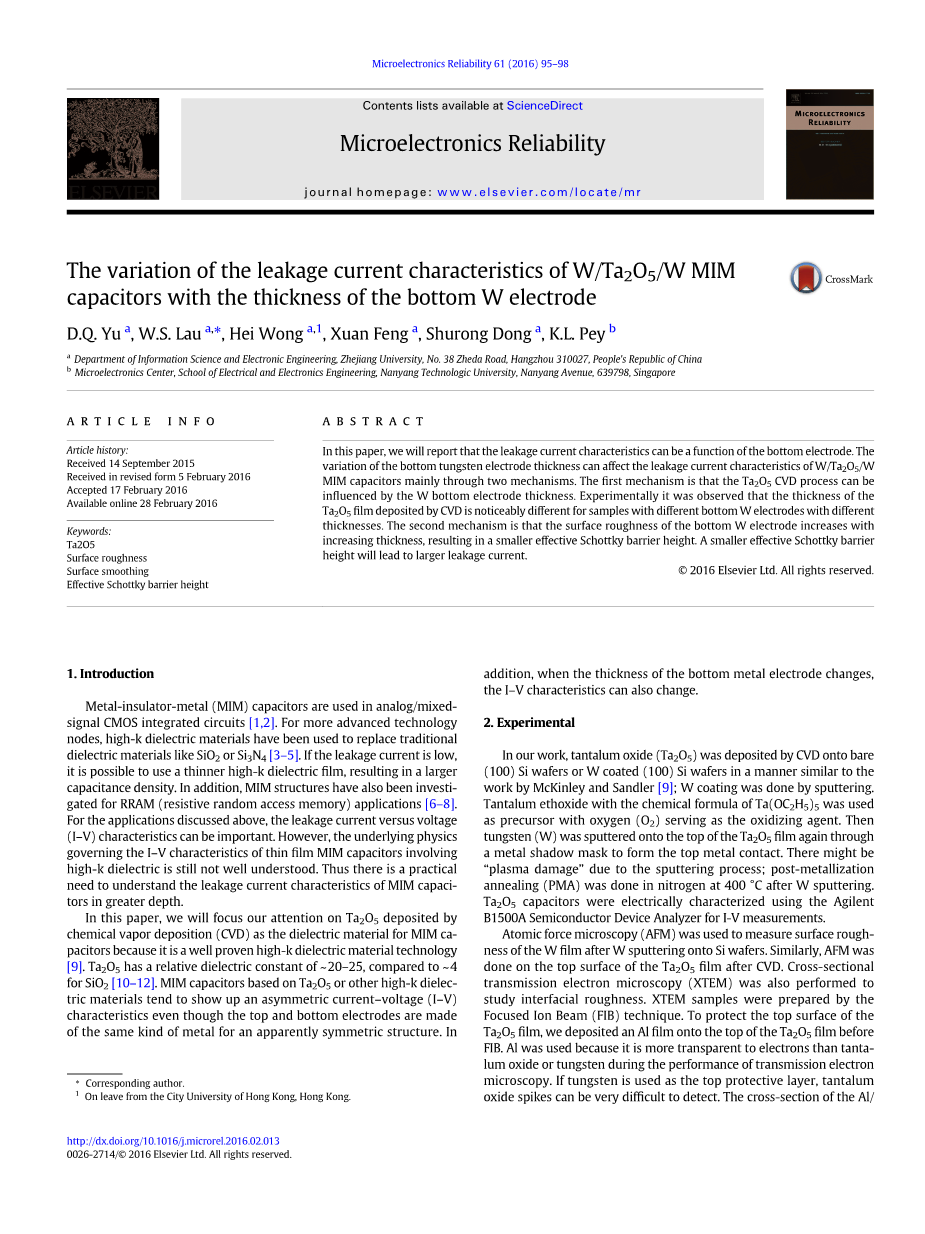

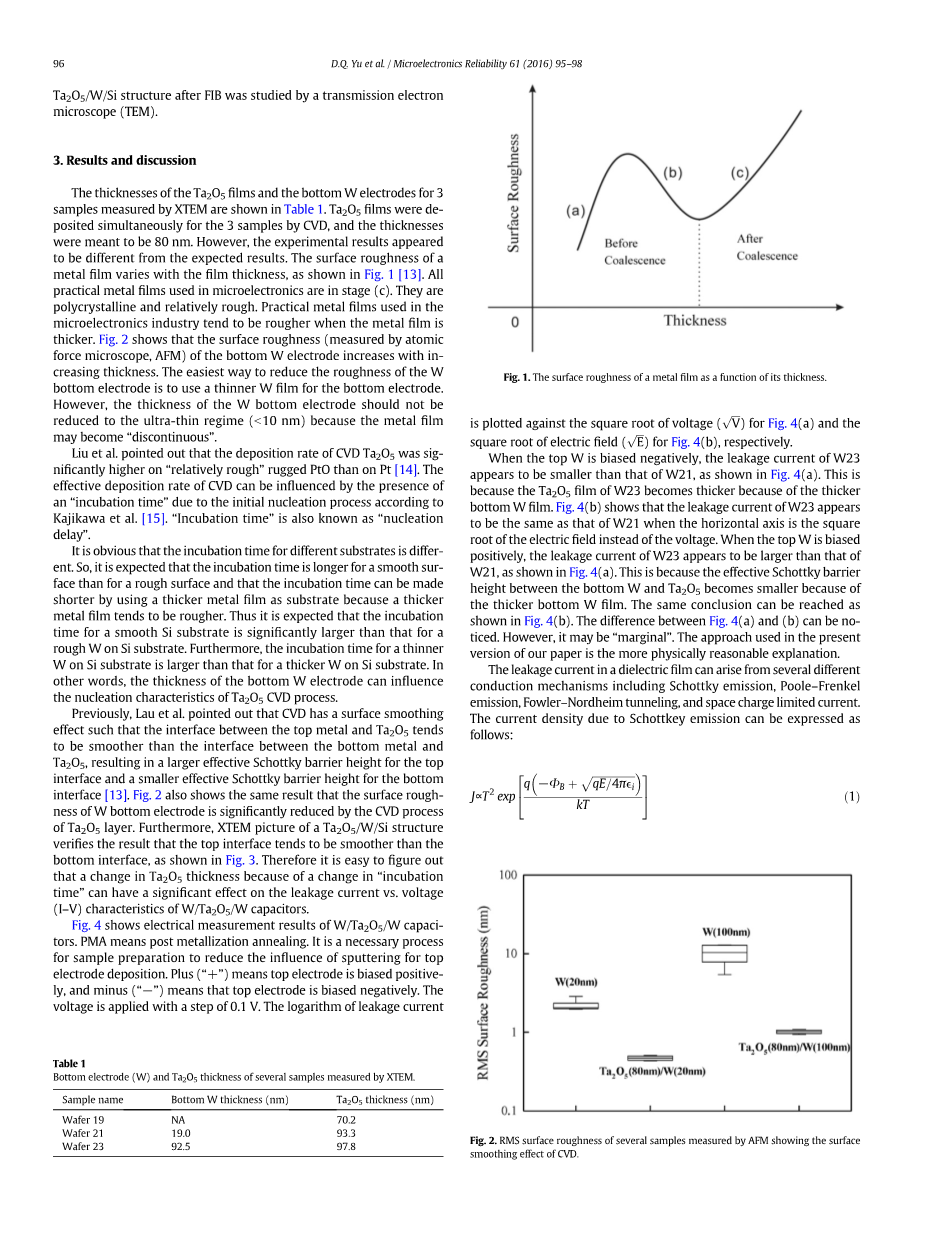

由XTEM测量的三片样品得到的Ta2O5薄膜和底部钨电极厚度的数据,如表1所示。沉积Ta2O5薄膜的同时对3个样品进行化学气相沉积并且厚度控制在80纳米。然而,实验出现了不同于预期的结果。表面粗糙度金属膜随膜厚度变化,如图1〔13〕所示。所有用于微电子的实用金属薄膜都处于阶段(C)。它们具有多晶且相对粗糙的特性。微电子工业中使用的实际金属膜往往更加粗糙当金属薄膜更厚时。图2展示了底部W电极的表面粗糙度(原子力显微镜、AFM测量)随厚度的增加而增加。降低W底电极粗糙度的最简单方法是使用较薄的W膜作为底部电极。然而,W底电极的厚度不应减少到超薄状态(B10nm),因为金属膜可能变成“不连续的”。

刘等人指出在相对粗糙的PTO上,CVD Ta2O5的沉积速率明显高于Pt〔14〕。根据Kajikawa等人的初始成核过程,CVD的有效沉积速率可以受到存在“孵育时间”的影响。“潜伏期”也称为“成核延迟”。

可见,不同基质的培养时间不同。因此,预期表面光滑时间比粗糙表面长,并且通过使用较厚的金属膜作为基底,可以使培养时间变短,因为较厚的金属膜倾向于粗糙。这样,预期平滑Si衬底的孵育时间显著大于粗糙硅衬底的孵育时间。此外,Si衬底上较薄W的孕育时间大于Si衬底上较厚W的孕育时间。换言之,底部W电极的厚度可以影响Ta2O5的CVD工艺的成核特性。

此前,刘等人指出CVD具有表面光滑效应,使得顶部金属和Ta2O5之间的界面趋向于比底部金属和Ta2O5之间的界面更光滑,从而导致顶部界面的更大的有效肖特基势垒高度和底部界面更小的有效肖特基势垒。图2也展示了Ta2O5层CVD工艺显著降低W底电极表面粗糙度的结果。另外,Ta2O5/W/Si结构的XTEM图验证了顶部界面趋向于比底部界面更光滑的结果,如图3。因此,很容易看出,由于“潜伏期”的变化,Ta2O5厚度的变化会对W/Ta2O5/W电容器的漏电流与电压(I-V)特性产生显著的影响。

图4展示了W/Ta2O5/W电容器的电测量结果。PMA是指金属化后退火。减少溅射对顶部电极沉积的影响是制样过程中必不可少的一个过程。正(“ ”)表示顶部电极正向偏置,负(“-”)意味着顶部电极负向偏压。施加电压为每步0.1V。漏电流对数是分别地对电压平方根进行开方(Vfrac12;)如图4和对电场进行开平方(Efrac12;)。

当W偏压为负时,W23的漏电流小于W21,如图4(a)所示。这是因为W23的Ta2O5薄膜由于较厚的底片而变厚。图4(b)说明了当水平轴是电场的平方根而不是电压时,W23的泄漏电流似乎与W21的泄漏电流相同。当W正向偏置时,W23的泄漏电流大于W21,如图4(a)所示。这是因为底部W和Ta2O5之间的有效肖特基势垒高度由于较厚的底部W膜而变小,同样的结论可以在图4(b)得到。图4(a)和图4(b)的区别能够被注意到。但是,它可能是“临界的”。在本论文的版本中使用的方法是更合理的物理解释。

介质膜中的泄漏电流可以由几种不同的传导机制产生,包括肖特基发射,普尔-弗伦克尔发射,福勒-诺德海姆隧穿和空间电荷限制电流。肖特基辐射引起的电流密度可如下方程表示: 。 (1)

另外,普尔-弗伦克尔机制引起的电流密度可以写为:

。 (2)

当J表示电流密度时,T代表绝对温度,K是玻尔兹曼常数,Q表示电子电荷,E代表电场,是势垒高度,表示绝缘体材料的介电常数。图5为金属绝缘体半导体结构肖特基发射和普尔 -弗伦克尔机制的能带图解【19-20】。

基于Ta2O5的MIM电容器漏电流主导机理的确定,还研究了介质在不同温度下的泄漏电流。图6可看出W21在不同温度下的I—V测量结果。通过研究肖特基发射方程和普尔-弗朗克尔机制,很明显,对于普尔-弗伦克尔机制,漏电流对数与电压平方根的曲线斜率比肖特基发射机制更大。当肖特基发射和普尔 -弗朗克尔机制串联时,很自然地,普尔 -弗朗克尔机制在低电压下主导肖特基发射,而肖特基发射在高压下占据普尔 -弗朗克尔机制。【20】在RT和高于4 V的电压下,泄漏电流机制是低电压下的普尔 -弗伦克尔和正偏压的高电压肖特基发射,泄漏电流机制在低偏压和高电压下都是肖特基发射,用于负偏压。(在非常低的电压下,I-V曲线是两种极化的欧姆曲线)在约350 K时,泄漏电流机制分别是普尔 -弗伦克尔在低电压和肖特基在高电压为正偏压,泄漏电流机制普尔-弗伦克尔在低电压和肖特基在高电压下负偏压。

4 结论

底部金属膜可影响漏电流Vs。高介电常数MIM电容器的两种电压特性:(1)底部金属膜可影响高介电质的沉积过程;(2)底部金属膜可以变得更粗糙更大的厚度,导致较小的有效势垒高度之间的底部金属膜和高介电常数。为了获得更稳定和理想的MIM电容器的电性能,应通过更先进的沉积工艺或膜厚减小来减小底部电极的表面粗糙度。

表格一:用XTEM测量了多个样品的底部电极(W)和Ta2O5的厚度。

|

样品编号 |

底部厚度(nm) |

Ta2O5厚度(nm) |

|

薄片19 |

NA |

70.2 |

|

薄片21 |

19.0 |

93.3 |

|

薄片23 |

92.5 |

97.8 |

图2.用AFM测量多个样品的RMS表面粗糙度,显示CVD的表面平滑效应

图3.Ta2O5/W/Si样品的XTEM显微照片(W厚度约为20nm,Ta2O5的厚度约为80nm。Al被用作保护层,因为在样品制备过程中使用了FIB。)

图4.在室温(约22°C)下的样品/Ta2O5/W的VI测量结果。

图5.(a)肖特基发射和(b)普尔-弗伦克尔辐射在金属-绝缘体-半导体结构上的示意能带图。

图6.在室温(约295 K)、320 K、350 K和380 K下的I—V测量结果。

5 参考文献

[1] K. Stein, J. Kocis, G. Hueckel, et al., High reliability metal insulator metal capacitors for silicon germanium analog applications, Bipolar/BiCMOS Circuits and Technology Meeting (IEEE) 1997, pp. 191–194.

[2] J. Babcock, S.G. Balster, A. Pinto, et al., Analog characteristics of metal-insulatormetal capacitors using PECVD nitride dielectrics, IEEE Electron. Dev. Lett. 22 (5)(2001) 230–232.

[3] C.S. Ho, S.J. Chang, S.C. Chen, et al., A reliable Si3N4/Al2O3–HfO2 stack MIM capacitor for high-voltage analog applications, IEEE Trans. Electron. Dev. 61 (8) (2014)2944–2949.

[4] Y. Nishioka, H. Shinriki, K. Mukai, Influence of SiO2 at the Ta2O5/Si interface on dielectric characteristics of Ta2O5 capacitors, J. Appl. Phys. 61 (6) (1987) 2335–2338.

[5] G.B. Alers, D.J. Werder, Y. Chabal, et al., Intermixing at the tantalum oxide/silicon interface in gate dielectric structures, A

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[464120],资料为PDF文档或Word文档,PDF文档可免费转换为Word