英语原文共 42 页,剩余内容已隐藏,支付完成后下载完整资料

章节11

粘晶材料和薄膜

摘要 本章概述了电子封装技术的发展与粘晶材料的所需特性之间的强相关性,概述了粘晶材料的市场发展趋势。芯片粘贴胶,芯片上引线(LOC)胶带,芯片粘贴膜和先进的芯片附着薄膜的前景在每个部分中都有描述。对芯片附着材料的技术要求进行讨论,其中包括高纯度,快速固化,低应力,高封装抗裂性和多芯片封装。

芯片附着膜因为其优良的性能和可靠性已成为芯片附着材料的主流,未来的先进芯片贴装薄膜是通过引入具有切割/芯片贴装双重功能的粘合剂薄膜来展现其功能。

详细报道了粘合性能如剥离强度和吸水性的影响,综述了微相分离结构用于多层包装工艺的芯片贴膜的发展,也介绍了下一代封装的粘晶材料的评估。

11.1 粘晶材料

11.1.1电子封装的趋势

本节概述了电子封装技术的发展,其一直是半导体行业研究的前沿。封装技术强烈影响粘晶材料的特性和指标,因此为了粘晶材料的发展充分了解包装技术对于我们来说非常重要,因为这些材料与包装方案密切相关。

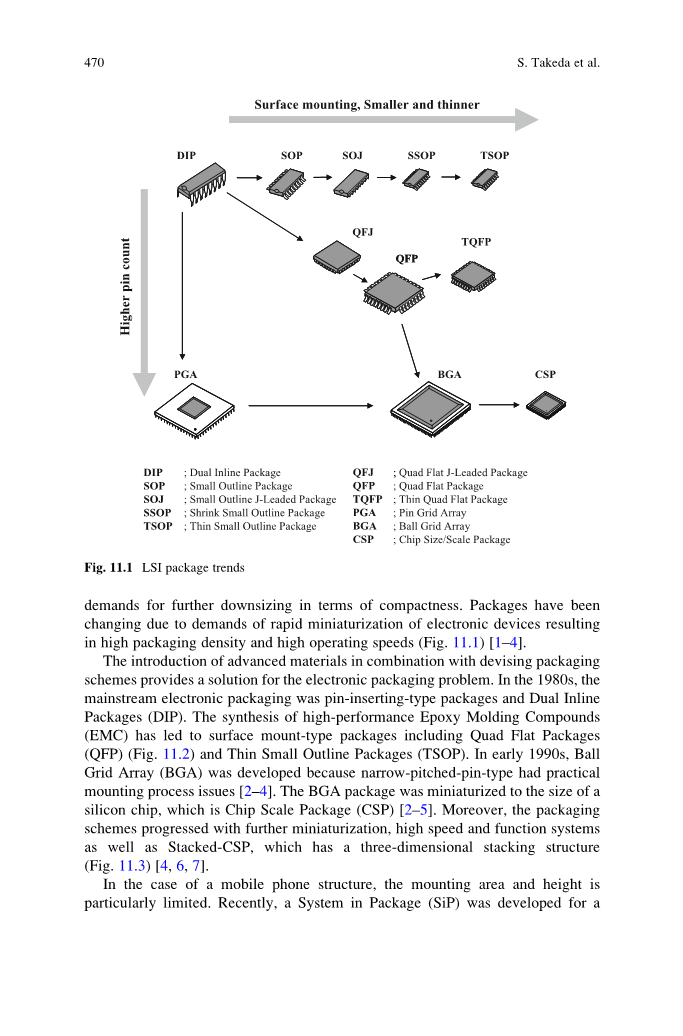

个人便携式设备日益增长的需求已经导致前所未有的市场竞争的提升,因此在紧凑性方面对进一步的小型化提出了很高的要求。由于要求电子设备快速小型化,因此封装一直在向高封装密度和高运行速度变化。

图11.1 LSI封装趋势

先进的材料和设计包装相结合的引入为电子封装问题提供了解决方案。在20世纪80年代,主流电子封装是引脚插入型封装和双列直插封装(DIP)。高性能环氧树脂成型化合物(EMC)的合成促成了表面贴装型封装,包括四扁平封装(QFP)和薄型小外形封装(TSOP)。在20世纪90年代早期,球栅阵列(BGA)的开发是因为窄间距针型有实际的安装过程问题。BGA封装被微型化为芯片尺寸封装(CSP)[2-5]的硅芯片尺寸。此外,电子包装小型化,高速化和功能化系统以及具有三维堆叠结构的Stacked-CSP将进一步发展。

就手机结构而言,芯片的安装面积和高度特别有限。最近,一种系统级封装(SiP)被开发用于手机,其具有堆叠在封装中的不同功能芯片,逻辑和存储器。堆叠封装类型的使用在手机技术中越来越多。

11.1.2粘晶材料的趋势

粘晶材料被用作硅芯片(管芯)和衬底之间的粘合剂。图11.4中的封装过程示出了传统的过程流程。芯片连接过程是集成芯片(IC)器件制造的重要组成部分,因为粘晶材料在半导体封装的可靠性和性能中起着关键作用。封装过程中的压倒性发展导致了芯片连接性能的后续改进和修改[1]。

粘晶材料,如金,焊料和聚合物粘合剂,如糊状物膜已被广泛使用。芯片连接的要求取决于包装的配置。20世纪80年代应用最广泛的芯片附着材料是金 - 硅(Au-Si)共晶体。在400℃时,硅晶片附着在镀金的铅框上产生共晶。由于管芯附着材料和衬底之间的热膨胀不匹配,高的芯片应力证明Au-Si是有问题的,而且经济因素也导致了Au-Si的下降,因为黄金价格大幅上涨,导致了对更便宜材料的需求[8-10]。

由于具有高导热性和脱水性,焊料是有利的,这些可靠性已被证明会随着性能而增强。焊料的均匀微观结构的形成也提高了对热疲劳失效的抵抗力[11]。

但是,焊料有许多缺点,焊料的应用包括使用助焊剂以确保良好的连接性,然后通过去焊工艺去除昂贵的并由于排放氯化物质而引起环境问题的焊剂。此外,高附着温度引起铜引线框架的氧化,这增加了芯片和框架之间的应力。

为了克服Au-Si共晶和焊料的问题,开发了银糊等聚合物粘合剂。

新合成的由银填料和树脂组成的糊剂成为现有材料的有吸引力的替代物。银浆(芯片粘贴)具有较低的相关成本和理想性能,包括较低的应力水平以及较低的加工温度。更多细节将在本章后面部分讨论。

11.1.3对粘晶材料的要求

粘晶材料的技术要求包括在回流时具有高纯度(低杂质含量),快速固化,低应力和高抗包装开裂特性。纯度要求不仅对粘晶材料至关重要,而且对大多数其他电子封装材料也很重要。据报道,微量的离子污染会导致铝在包装中的腐蚀[12]。在银浆开发的早期阶段,易受污染是一个主要的技术问题。这种污染问题通过原材料和基础树脂的纯化以及特殊复合技术的引入而得到解决。

短的固化时间对于通过在线固化工艺来实现高生产量是非常重要的。短的固化时间对于通过在线固化工艺实现高生产量是非常重要的。关于银浆,需要室温稳定性和快速固化(小于2分钟)。选择和优化固化剂和加速剂以实现快速固化。 然而,银浆形式的粘合剂在固化过程中经常会形成空隙,这些空隙降低了包装的可靠性,并且仍然是银浆应用的紧迫问题[9]。

低压力是先进包装系统的另一个基本要求。当IC芯片连接在表面上的电路的铜引线框架或聚合物基板如玻璃环氧树脂和聚酰亚胺上时,硅芯片和衬底之间的CTE(热膨胀系数)不匹配会引起翘曲并产生内部应力(图11.5)。通过使用低应力粘晶材料可以缓解压力[13,14]。

随着半导体封装向更高集成度和更高引脚数发展,封装抗裂性是粘晶材料的另一个关键特性。这需要更小更薄封装的大尺寸芯片,因此在系统的高效运行中必须具备抗裂性能。与表面安装器件有关的一个主要可靠性问题是由焊接应力引起的封装开裂,通常是由于将整个封装暴露在高达240-260℃的温度下。回流焊接过程中的封装开裂阻力机理在本节中介绍。尽管如此,芯片粘结薄膜有助于克服这些问题[15-17]。

近年来,由于铅中毒和环境污染问题日益严重,无铅焊接已经成为电子行业的全球趋势。由于无铅焊料的熔点较高,回流焊温度显著上升。较高的回流温度对目前的粘晶材料造成了非常严重的问题,特别是在封装抗裂性方面。

11.1.4粘晶膏

粘晶膏由诸如银,氧化铝和二氧化硅的填充剂以及诸如环氧树脂,聚酰亚胺,聚丙烯酸酯和硅树脂的基础树脂组成。将填料分散在室温下具有适合的加工性的充分流动性的碱性树脂中,然后通过加热将粘晶膏固化以将硅芯片固定在引线框架上。大部分管芯粘贴膏是由银填料和环氧树脂组成的银膏。银填料具有独特的薄片形状,平均尺寸为2-10微米,由于片状填料及其表面涂层试剂,银浆需要具有良好的铺展性和理想的流变性[11]。

为了在硅芯片和聚合物衬底上的电图案之间保持绝缘,使用包含二氧化硅作为填充物的绝缘填充膏用于包括BGA,堆叠CSP的高级封装。

如图11.6所示,插图描绘了涉及三个主要阶段的模具连接过程,即分配,附着和固化[9,11]。在芯片贴附工艺中存在实际的挑战,例如,低粘度糊状物的渗出,高粘度糊状物的铺展性,包含低沸点溶剂的糊状物的干燥性以及糊状物与反应性稀释试剂的脱气。

最受欢迎的基础树脂是一种环氧树脂体系,它表现出良好的粘合强度并显示出作为粘晶材料的理想性能。因为树脂是由表氯醇和苯酚钠合成的,所以早期的环氧树脂中含有氯和钠等污染物,由于高度纯化的材料是为该半导体领域开发的,所以污染问题得到解决[18]。

二十世纪九十年代开发了一种使用聚丙烯酸酯作为基础树脂的芯片粘贴膏,聚丙烯酸酯糊剂的优点包括由于自由基聚合引起的快速固化速度(1-2分钟固化),由于稳定的过氧化物引发剂而具有较长的保存期限以及由于低粘度材料(丙烯酸酯单体)而具有良好的处理性能。

最近,粘晶材料制造商正在开发各种糊剂以满足特定的客户要求。客户可能要求具有较强粘合强度和较低吸湿性的耐回流焊膏,具有高含量填料的高导热导电膏和对每种要求均适合其各自应用而具有无空隙和低应力的非溶剂型膏[18]。

11.1.5LOC包装用胶带

LOC(芯片上引线)封装使用胶带,如图11.7所示[10,19,20]。由于引脚位于硅芯片之上的LOC封装的结构,LOC封装小于诸如QFP(四方扁平封装)的标准封装,内引线通过胶带附着在芯片的表面上。LOC封装的结构适合于高密度安装,并且适用于DRAM(动态随机存取存储器)[19,20]领域的TSOP(薄型小外形封装)。

用于LOC的胶带的基础树脂是聚酰亚胺,并且胶带由三个主层组成[10,19,20]。粘合剂涂布在聚酰亚胺薄膜的两侧。胶带含有热熔粘合剂,它在200-400℃的高温和10-30N /芯片的高压下连接,由于胶带直接附着在硅片表面上,所以高纯度,低释气和高耐热性是重要的,为了降低粘合剂加工温度,开发了各种聚合物结构,并将柔性链段引入硬聚合物分子主链[19,20]。

11.1.6芯片粘结薄膜

芯片粘结薄膜已成为实现具有高可靠性和高性能的更小,更薄,高密度封装的关键技术。

DuPontreg;于1988年发布了一种由热塑性树脂和银填料组成的贴片膜[21]。NittoDenkoreg;提出了一种新的概念,这是一种在1991年减少了加工步骤的数量芯片附着切割薄膜[22]。

在1994年,日立化学开发出了一种新型贴片膜“HIATTACH”,它能够在低温低压下,在短时间内(短时间内)附着芯片,并且在回流焊接过程中也表现出出色的封装抗裂性能[23,24]。芯片贴装薄膜大大改善了器件的可靠性,此外,还开发了一种新的芯片贴装工艺,其中包括一个新的芯片贴装薄膜贴片机,该贴装机完全不同于芯片粘贴贴片工艺(图11.8)。

一些制造商在1997年开发了低应力芯片贴膜,以满足先进封装的要求。在芯片附着薄膜的生产方面已经有了重大的发展,并且在这个领域正在进行的研究对于电子封装工业来说至关重要。更多细节将在下一节讨论。

11.1.7 先进的芯片粘结薄膜的未来

11.1.7.1 用于先进BGA / CSP的贴片膜

芯片阵列封装(MAP)能够减少工艺数量,从而降低成本[25]。先进BGA / CSP的规模在不断增加,并导致各种技术问题。主要问题是由于衬底,焊球和印刷电路板组成的结构中的材料的CTE不匹配,衬底的大翘曲和封装内部/外部的连接性差[25]。在这个领域中,芯片贴膜的最重要的要求是减小封装的应力,低附着温度和低模量的芯片附着膜正在开发中,以满足先进BGA / CSP的上述要求[26,27]。

11.1.7.2切割/晶粒附着双功能膜

其中堆叠多个芯片的堆叠式多芯片封装(Stacked-MCP;图11.3)已经被广泛关注,并且由于对先进封装的要求越来越小,越来越薄并且性能越来越高[28,29]。堆叠MCP的芯片附着膜的要求包括制造步骤的减少和易于处理更薄的晶圆。为了满足这些要求,2005年开发并推出了一种切割/模片连接双功能薄膜[30,31],该膜由两层组成,即UV反应型切割膜和热固型芯片附着膜。

图11.9显示了传统的堆叠MCP制造工艺,对于切割膜和管芯附着膜来说,两个层压步骤是必需的。图11.10显示了堆叠包装的新过程,切割/芯片贴装膜通过一个步骤层压。这种双功能薄膜实现了减少制造步骤的数量,并在加工过程中轻松处理更薄的晶圆[30]。

11.1.7.3用于多层包装工艺的芯片粘结膜

电子设备的最新进展需要更紧凑,更轻,功能更强的组件。芯片接合薄膜广泛用于智能手机,个人电脑等电子设备的半导体封装。用于这种器件的芯片接合薄膜的要求包括高粘合强度和耐热性。为了满足上述要求,选择了基于反应诱导相分解的丙烯酸类聚合物 - 基体环氧粘合剂。基于这些聚合物基体系统的芯片结合膜在热循环测试期间的热应力下显示出比基于环氧基体系统的膜更高的柔韧性。另外,根据环氧树脂和丙烯酸类聚合物的含量的比例,聚合物基体类膜的性质差别很大。 为了满足目标特性,开发了一种新的材料设计方法--弱条件组合线性规划,可以使用新开发的用户友好软件进行通过此方法的优化。

诸如智能手机(图11.11),平板电脑,超薄笔记本电脑和支持云存储的服务器等先进电子设备正在不断发展,如图11.11所示,半导体封装是这些器件的核心,并且也在迅速发展。

各种材料用于半导体,近年来,多层半导体封装一直是提高电子器件性能的最重要技术之一。为了满足电子器件的复杂要求,单位面积上的半导体安装密度必须增加,需要使用高性能材料的新型封装方法。为了结合多芯片封装的每一层,芯片接合膜被广泛使用。例如,如图11.12所示,在半导体封装中使用了几种类型的芯片接合膜,因此,对于电影的要求根据应用而变化。图11.13显示了制造堆叠封装的工艺和芯片焊接薄膜的要求。半导体封装的组装过程也是多样化的,并且每个过程都需要各种属性。 通常需要的属性包括以下内容:

- 薄膜必须在60-80℃的温度范围内发粘,并且必须能够粘附在晶圆上。

-

由于薄膜用于将芯片粘合到基板上,它必

全文共7443字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[9728],资料为PDF文档或Word文档,PDF文档可免费转换为Word